# System-Level Design Space Exploration for SoCs Integrating Optical Networks on Chip

Fabiano Hessel<sup>1</sup>, Gabriela Nicolescu<sup>2</sup>, Odile Liboirin-Ladouceur<sup>3</sup>, Felipe de Magalhaes<sup>1,2</sup>

<sup>1</sup>PUCRS Brazil, <sup>2</sup>Polytechnique Montréal Canada <sup>3</sup>McGill University

March 2015 1st OPTICS Workshop

# Multi-Processor Systems-on-Chip (MPSoC) Design Trends

#### SoC Design – two contradictory trends

- Rising platform development cost

- ☐ Embedded software over 50% of the total cost

- □ Complexity increasing with 140% per year

- Reducing the product market window

#### Directions to tackle these challenges

- Exploit domain-specific MPSoC reusable platforms

- Several interconnected processors

- Networks-on-Chip

### Classical Network-on-Chip Issues

- High power consumption

- Limited bandwidth

- Long latency

- Poor scalability

Studies have shown that global metallic interconnects will consume kilowatts of power to achieve the communication bandwidth that will be required by MPSoCs by 2020 using the 14 nm process

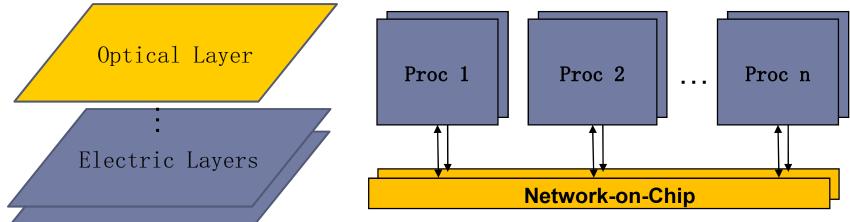

# Multi-Processor Systems-on-Chip (MPSoC) Design Trends

- Integration of Heterogeneous Technologies

- Promising paradigm

- Multiple technologies

- Functions will use the best technology available

- Ex. computing → electronics / communication → optics

# Multi-Processor Systems-on-Chip (MPSoC) Design Trends

- Integration of Heterogeneous Technologies

- Promising paradigm

4

- Multiple technologies

- Functions will use the best technology available

Ex. computing → electronics / communication → optics

Optical Layer

Pro

High Bandwidth

Low Power

Low latency

Netwo k-on-Chip

## Optical Integration Today

- ▶ Intel

- Integration of high-speed switches and optical fabrics

- ▶ HP

- MACHINE project

- approximately 75% of the researchers involved

- silicon photonics is employed to link a multicore system—on—chip to a bank of memristor memory cards

- ▶ IBM

- ▶ \$3 Billion Research Initiative to Tackle Chip Grand Challenges for Cloud and Big Data Systems

- □ Silicon Photonics is one of the explored technologies

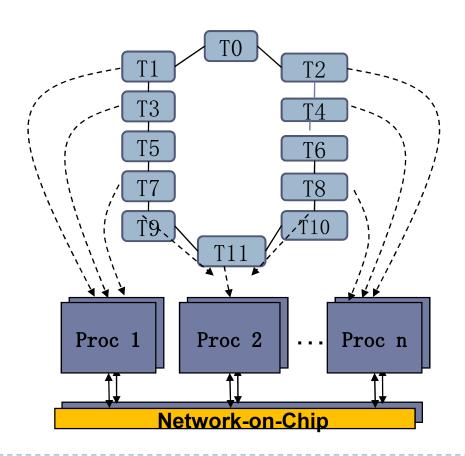

# Configuration Parameters in MPSoC Design

- Type of Network on Chip

- Type of routing

- Type of processors

- No. of proc. in the architecture

- No. of proc. per layer (tier)

- No. of layers (tiers)

- Technology used for each layer

- Application Mapping

# Configuration Parameters in MPSoC Design

- Huge solutions space

- Fast and accurate systemlevel tools for design-space exploration are mandatory

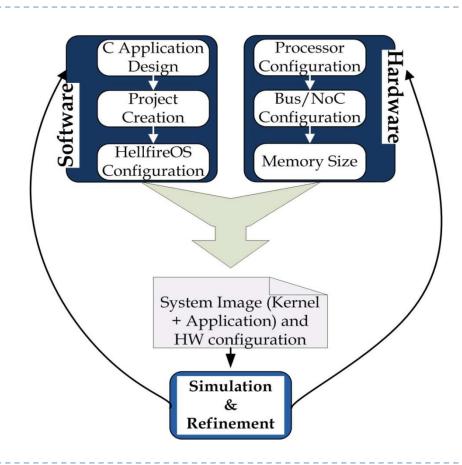

# Integrating Optical Network on chip Models to an existing System-Level Platform

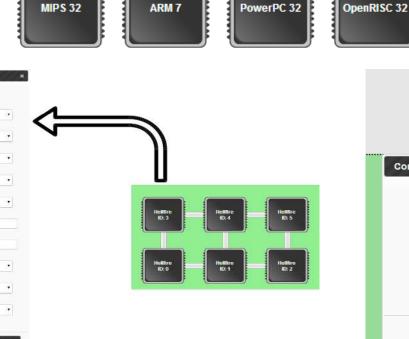

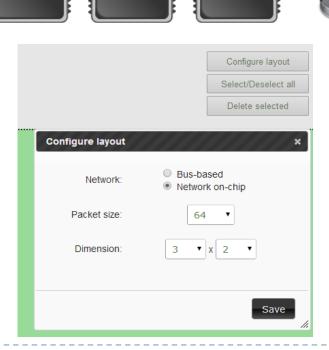

### ▶ HellFire Framework

- Proposed design-flow for the deployment of embedded applications

- Set of tools to aid the designer on the project

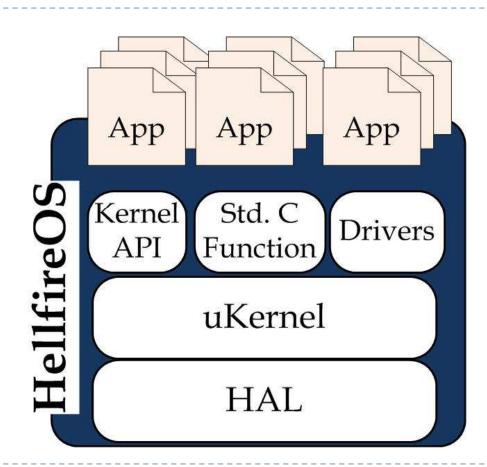

- ▶ HellfireOS

- ▶ Simulator

- ▶ Web-GUI

# Integrating Optical Network on chip Models to an existing System-Level Platform

### ▶ HellFireOS

- ▶ Modular Structure

- ▶ POSIX Like

- ▶ Real-time support

- Easily portable

- Parametrizable

- Stack size (each task)

- Heap size

- Number of user tasks

- Tick size

- Scheduling police

# Integrating Optical Network on chip Models to an existing System-Level Platform

Hellfire GUI

and

Frequency.

User Max Tasks:

Task Migration. No.

Enable Tasks Log No

Hellfire

μBlaze

## The next step

- Research is technology-dominated

- Physical level research

- New devices and architectures are defined

- System-level vision required

- Optical engineers

- Computer engineers

- Computer scientists

- Multi-disciplinary project

# The next step

- Nowadays describing methods are well suited for optical components

- ▶ Focus on improving those methods for better express the interactions for an entire system

- Extend available tools in order to provide real-time feedback

- Available models don't work well on real case scenarios, not expressing variations, like cross-talk and heating dissipation

- Speed X Accuracy

- Find a reliable and yet computationally feasible method for measuring dynamic system variations

# The next step

### ▶ Final Goal

- Provide a tool for the complete design of Opticalbased MPSoCs

- ▶ Library of switches, routers and pre-defined networks

- Dynamic behaviour of components and devices

- ▶ High-speed simulator

- ▶ High-level programming support through an embedded OS

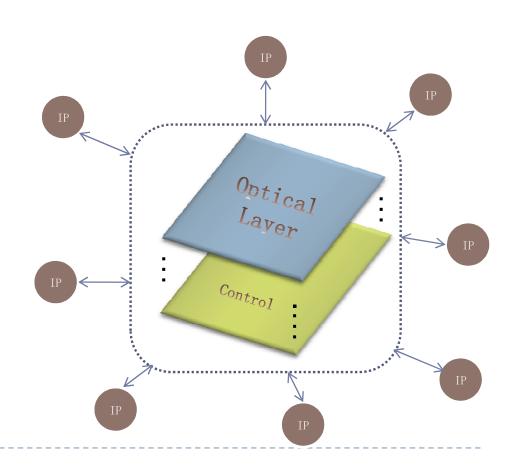

- ▶ Optical Network simulator

- Based on a in-house network model

- ▶ Connects eight IPs

- Composed by five MZI-based switches

- ▶ Electronic control layer

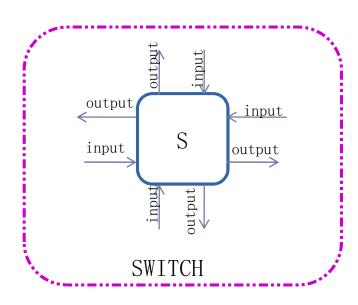

- ▶ MZI-based switch

- ▶ 4x4 switch

- Prototyped for data extraction

- ▶ Low delay design (20 ps)

- Wavelength based switching

- Network modeled in RLT level (VHDL)

- Integrated with a MIPS-like processor

- High-level support available through HFOS

```

Hardware Abstraction Layer (HAL)

#define NOC READ

0xf8000010

#define NOC WRITE

0xf8000020

#define NOC STATUS

0xf8000030

#define NOC DEST

0xf8000040

for (1=0; 1<PACKET SIZE; 1++) {

status = HF CriticalBegin();

HF task[0].packet in->data[1] = (wint16 t) MemoryRead(NOC READ);

MemoryWrite(NOC DEST, target cpu);

for (1=0:1<PACKET SIZE:1++)

MemoryWrite(NOC WRITE, HF task[task id].packet out->data[1]);

source cpu = HF task[0].packet in->data[0];

HF CriticalEnd(status);

task = HF task[0].packet in->data[1];

msg size = HF task[0].packet in->data[2];

HF task[task id].packets sent++;

HF task[HF CurrentTaskId()].comm busy = 0;

seq = HF task[0].packet in->data[3];

control = HF task[0].packet in->data[4];

HF SemPost (&pktdrv mutex);

crc = HF task[0].packet in->data[5];

send

receive

```

### ▶ Network + HFOS

```

void task_send(void){

uint8 t buf[30] = "hello!";

uint16 t dest = HF CurrentCpuId() + 1;

while (1) {

HF Send(dest, 2, buf, sizeof(buf));

printf("\nnode %d to node %d", HF CurrentCpuId(), dest);

HF TaskYield();

Welcome to the HF-RISC Bootloader - Apr 24 2014 19:49:47

Embedded Systems Group - GSE, PUCRS - [2006 - 2014]

HellfireOS RT Lite v1.4

Jun 19 2014, 17:04:34 (gcc 4.6.1)

Embedded Systems Group - GSE, PUCRS - [2007 - 2014]

CPU ID:

HF-RISC

Architecture:

Clock frequency:

25000 kHz

10485 us

System tick time:

TCB entry size:

224 bytes

TCB size:

1120 bytes

65535 bytes

Heap size:

Packet buffer size:

128 flits in sw FIFOs (each task), 32 flits in /

out hw FIFOs

Message delivery:

no ack

Maximum tasks:

node 1 to node 2

```

```

void task recv(void) {

uint16 t source cpu;

uint8 t source id;

uint16 t size;

uint8 t buf[31];

while (1) {

HF Receive (&source cpu, &source id, buf, &size);

printf("\nthread %d -> message from node %d thread %d size %d -> %s"

, HF CurrentTaskId(), source cpu, source id, size, buf);

HF TaskYield();

Welcome to the HF-RISC Bootloader - Apr 24 2014 19:49:47

Embedded Systems Group - GSE, PUCRS - [2006 - 2014]

HellfireOS RT Lite v1.4

Jun 19 2014, 17:04:36 (gcc 4.6.1)

Embedded Systems Group - GSE, PUCRS - [2007 - 2014]

CPU ID:

Architecture:

HF-RISC

Clock frequency:

25000 kHz

System tick time:

10485 us

TCB entry size:

224 bytes

TCB size:

1120 bytes

65535 bytes

Heap size:

128 flits in sw FIFOs (each task), 32 flits in /

Packet buffer size:

out hw FIFOs

Message delivery:

no ack

Maximum tasks:

thread 2 -> message from node 1 thread 2 size 30 -> hello!

thread 2 -> message from node 1 thread 2 size 30 -> hello!

thread 2 -> message from node 1 thread 2 size 30 -> hello!

thread 2 -> message from node 1 thread 2 size 30 -> hello!

thread 2 -> message from node 1 thread 2 size 30 -> hello!

thread 2 -> message from node 1 thread 2 size 30 -> hello!

```

### CONCLUSIONS

- Standard NoC implementations shows important drawbacks

- ▶ Optical-NoC cames as a possible solution

- Design methods for basic devices well matured

- ▶ Lack of tools for system—level design

- Extension of HFFW

# Multi-disciplinary Project Team

- Prof. Fabiano Hessel

- System-level platform for electronic systems design

- ▶ <u>fabiano.hessel@pucrs.br</u>

- http://www.inf.pucrs.br/gse

- Prof. Gabriela Nicolescu

- System-level modeling of optical-based environments

- gabriela.nicolescu@polymtl.ca

- https://sites.google.com/site/gnicolescuepm/home

- ▶ Prof. Odile Liboirin-Ladouceur

- Photonics physical level design

- ▶ <u>odile.liboiron-ladouceur@mcgill.ca</u>

- http://erbium.ece.mcgill.ca

# SYSTEM-LEVEL DESIGN SPACE EXPLORATION FOR SOCS INTEGRATING OPTICAL NETWORKS ON CHIP

Fabiano Hessel, Gabriela Nicolescu, Odile Liboirin-Ladouceur, Felipe de Magalhaes

March 2015 1st OPTICS Workshop