# Modelling and Analysis of Off-Chip Optical and Electrical Interconnect and Interface

Jiang Xu

## Acknowledgement

#### Current PhD students

Zhehui Wang, Duong Huu Kinh Luan, Peng Yang, Zhe Wang, Haoran Li, Zhifei Wang, Rafael Kioji Vivas Maeda, Xuanqi Chen, Zhongyuan Tian

#### Past members and visitors

Xuan Wang, Mahdi Nikdast, Yaoyao Ye, Xiaowen Wu, Weichen Liu, Xing Wen, Kwai Hung Mo, Yu Wang, Sébastien Le Beux, Yiyuan Xie, Huaxi Gu

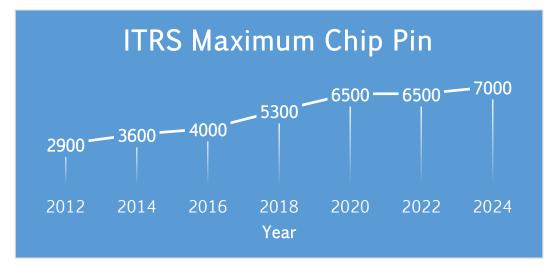

## Challenges of Inter/Intra-Chip Electrical Interconnect

- More communications from more cores

- Cisco QuantumFlow (40), Intel Phi (72), Tilera Tile (72), PicoChip (300) ...

- Blade server, micro server, disaggregated server ...

- Tighter I/O bandwidth

- Maximum pin count of package grows slow

- Higher packaging and PCB cost

- Larger latency

- Multiple clock cycles are required to cross a chip

- Higher energy consumption and loss

- Dynamic and leakage power of drivers and buffers

- ~35dB/m @12.5G on high-quality PCB

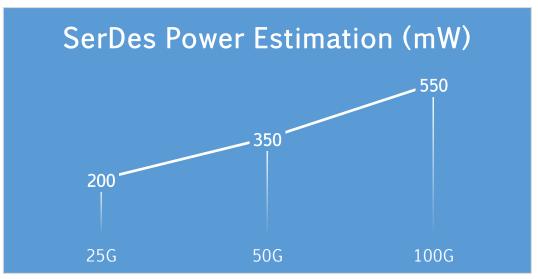

- SerDes energy and performance bottleneck

- ~5pJ/bit @ 100G

#### Optical Interconnect

- Photonic technologies have been successfully used in WAN and LAN

- Showed strengths in multicomputer systems and Internet core routers

- Benefit from more matured silicon-based technologies

- Micron-scale devices working at picosecond-level are widely demonstrated

- Commercialization efforts

- IBM, Intel (Omni-Path), HP (Machine), Oracle (UNIC), STMicro, NTT, NEC, Fujitsu (PECST), Huawei ...

- Startups: Luxtera-STMicro, Lightwire/Cisco, Kotura/Mellanox, Caliopa/Huawei, Aurrion, OneChip, Skorpios ...

- EDA: Cadence-PhoeniX-Lumerical, Mentor Graphics-Lumerical, RSoft/Synopsys ...

- Questions remain: What? How? & Why?

#### Integrated OE Interfaces & Processor

C. Sun *et al.*, "Single-chip microprocessor that communicates directly using light", Nature 2015

#### Integrated OE Interfaces

D.M. Gill, et al., "Demonstration of Error Free Operation Up To 32 Gb/s From a CMOS Integrated Monolithic Nano-Photonic Transmitter". CLEO 2015

#### Integrated Optical Switches

R. Ji, J. Xu, L. Yang, "Five-Port Optical Router Based on Microring Switches for Photonic Networks-on-Chip", IEEE Photonics Technology Letters, March, 2013

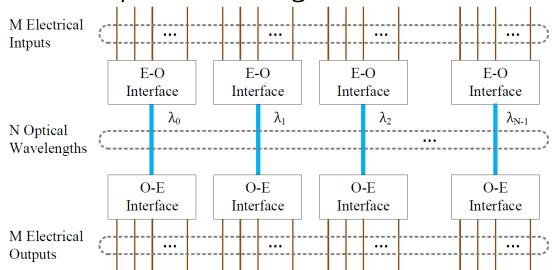

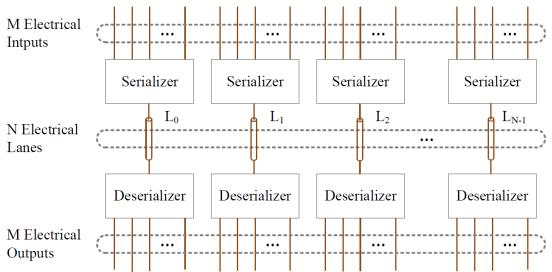

#### Off-Chip Interconnect Overview

- Optical interconnect OI(M,N) include

- M electrical inputs

- M electrical outputs

- N optical wavelengths

- Electrical interconnect EI(M,N) include

- M electrical inputs

- M electrical outputs

- N electrical lanes

<sup>\*</sup> Zhehui Wang, Jiang Xu, et al, "A Holistic Modelling and Analysis of Optical-Electrical Interfaces for Inter/Intra-chip Interconnects," IEEE TVLSI 2016

<sup>\*</sup> Zhehui Wang, Jiang Xu, et al, "Improve Chip Pin Performance Using Optical Interconnects," IEEE TVLSI 2015

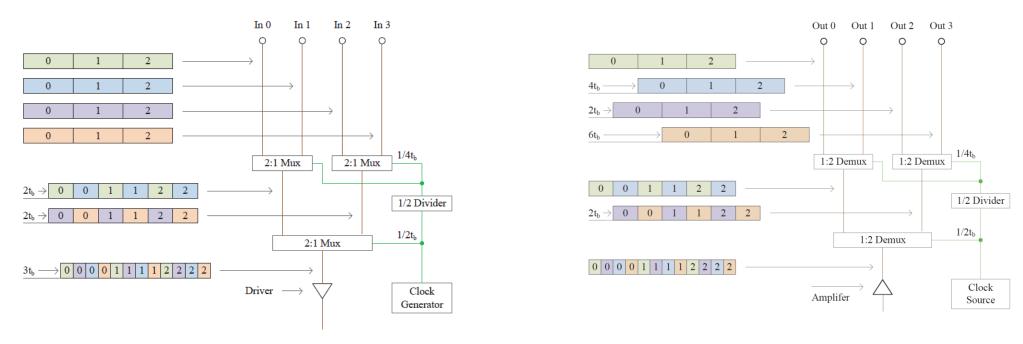

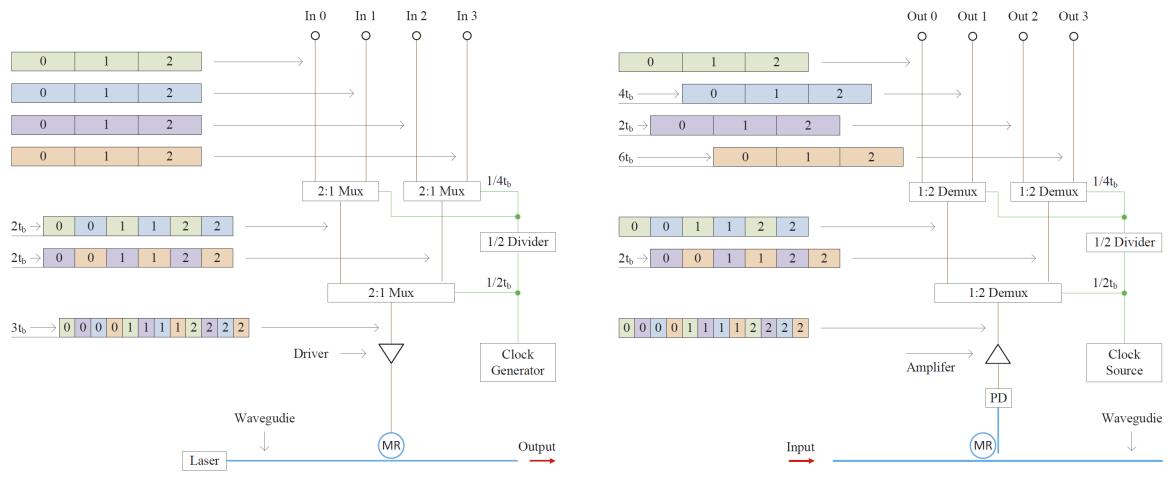

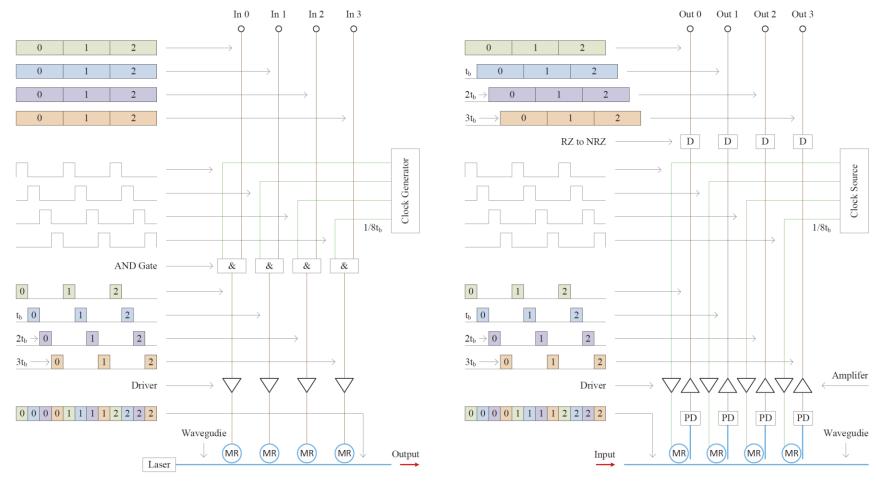

#### Off-Chip Interconnect Structure Examples

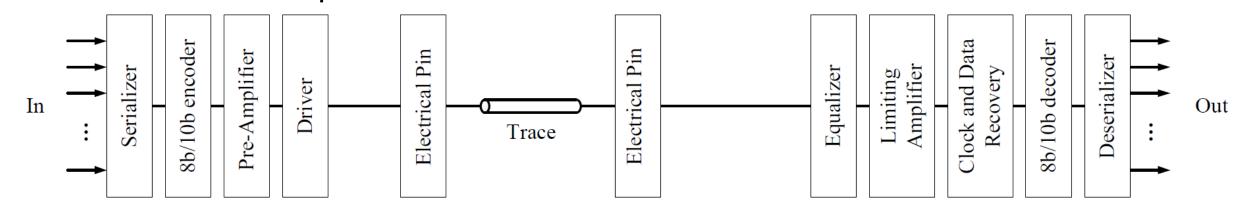

• Electrical off-chip Interconnect

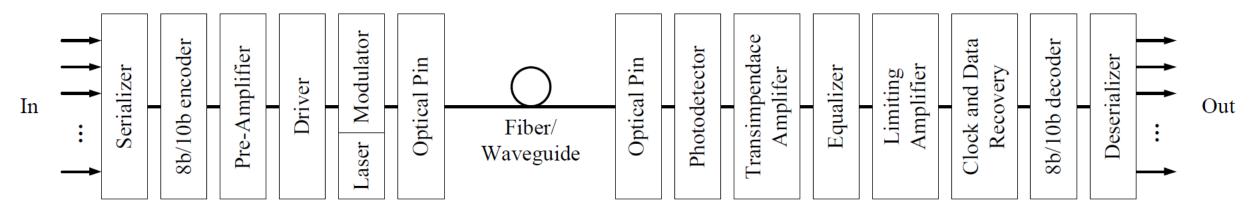

Optical off-chip Interconnect

## Holistic Models and Comparisons

- Optical interconnects vs. electrical Interconnects

- Bandwidth

- Area and linear bandwidth density

- Latency

- Energy efficiency

- Signal integrity

- Area

- OE interfaces

- SerDes designs

- Packaging options

- Different structures

#### Outline

- Introduction

- Modelling off-chip interconnects and interfaces

- Electrical Interconnects

- Optical Interconnects

- SerDes and O-E interface

- A new O-E interface

- Quantitative analysis and comparisons

- Conclusions

## Basic Design Parameters

|                                          | Saraswat | Chen | Esener | OEIL |

|------------------------------------------|----------|------|--------|------|

| 1 Energy Efficiency                      |          |      | ✓      | ✓    |

| 1.1 Power Consumption                    | ✓        | ✓    | ✓      | ✓    |

| 1.1.1 Transmitter Power                  | ✓        | *    | ✓      | ✓    |

| 1.1.1.1 Crosstalk Noise                  |          |      |        | ✓    |

| 1.1.1.1.1 Number of Wavelengths          |          |      |        | ✓    |

| 1.1.1.1.2 Wavelength Spacing             |          |      |        | ✓    |

| 1.1.1.1.3 MR Characteristics             |          |      |        | ✓    |

| 1.1.1.2 Optical Power Loss               |          |      | ✓      | ✓    |

| 1.1.1.2.1 Coupler Loss                   |          |      |        | ✓    |

| 1.1.1.2.2 Waveguide Attenuation          |          |      |        | ✓    |

| 1.1.1.2.3 Interconnect Length            |          |      |        | ✓    |

| 1.1.1.2.4 MR Characteristics             | ✓        |      |        | ✓    |

| 1.1.1.3 Receiver Sensitivity             | ✓        |      |        | ✓    |

| 1.1.1.3.1 Photodetector Responsively     | *        |      |        | ✓    |

| 1.1.1.3.2 Signal to Noise Ratio          | *        |      |        | ✓    |

| 1.1.1.3.3 Modulation Frequency           | *        |      |        | ✓    |

| 1.1.1.3.4 TIA Transimpedance             |          |      |        | ✓    |

| 1.1.1.3.5 Limiting Amplifier Sensitivity |          |      |        | ✓    |

| 1.1.1.4 Laser & Modulator Parameters     | ✓        | *    | *      | ✓    |

| 1.1.1.4.1 Threshold Current              |          |      | *      | ✓    |

| 1.1.1.4.2 Slope Efficiency               | ✓        |      | ✓      | ✓    |

| 1.1.1.4.3 Power Extinction Ratio         | ✓        | *    | ✓      | ✓    |

|                                     | Saraswat | Chen | Esener | OEIL |

|-------------------------------------|----------|------|--------|------|

| 1.1.2 Receiver Power                | *        | ✓    | ✓      | ✓    |

| 1.1.2.1 TIA Power                   | *        | ✓    | ✓      | ✓    |

| 1.1.2.1.1 Photodetector Capacitance | *        |      | ✓      | ✓    |

| 1.1.2.1.2 Signal Frequency          | *        |      |        | ✓    |

| 1.1.2.1.3 TIA Supply Voltage        |          | ✓    | ✓      | ✓    |

| 1.1.2.2 LA Power                    | *        | ✓    | ✓      | ✓    |

| 1.1.2.2.1 LA Supply Current         |          | ✓    | ✓      | ✓    |

| 1.1.2.2.2 LA Supply Voltage         |          | ✓    | ✓      | ✓    |

| 1.2 Data Rate                       | *        |      |        | ✓    |

| 2 Bandwidth Density                 |          | *    |        | ✓    |

| 2.1 Data Rate per Wavelength        |          | *    |        | ✓    |

| 2.2 Number of Wavelengths           |          | *    |        | ✓    |

| 2.2.1 MR Characteristics            |          |      |        | ✓    |

| 2.2.2 Wavelength Spacing            |          |      |        | ✓    |

| 2.3 Optical Pin Pitch               |          |      |        | ✓    |

| 2.4 Waveguide Pitch                 |          | ✓    |        | ✓    |

| 3 Latency                           |          | ✓    |        | ✓    |

| 3.1 RC Delay                        |          | ✓    |        | ✓    |

| 3.2 Propagation Delay               |          | *    |        | ✓    |

| 3.2.1 Interconnect Length           |          |      |        | ✓    |

| 3.2.2 Signal Propagation Speed      |          | *    |        | ✓    |

<sup>\*</sup> Mentioned but without an exact model

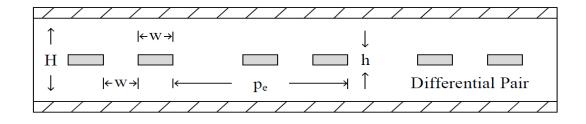

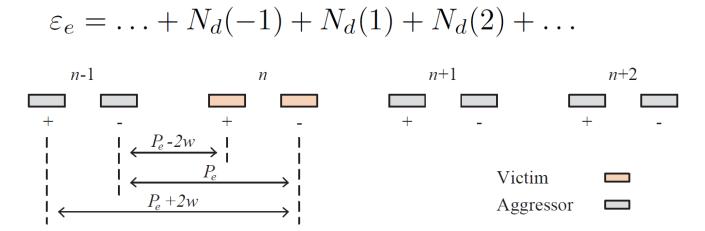

#### **Electrical Crosstalk Noise**

- Top/bottom layer for power/ground and inner layer for signal

- The differential traces on PCB board has the following parameters:

- H height between two panels

- w width of a trace

- *h* height of a trace

- *P<sub>e</sub>* pitch of differential traces:

• C(d) is the crosstalk noise coefficient of two traces with distance d

$$c(d) = H^2/(4d^2 + H^2)$$

#### Electrical Crosstalk Noise

N<sub>d</sub>(i) is the crosstalk noise coefficient between two differential pair n and pair n+i

$$N_d(i) = c(|i|p_e - 2w) - 2c(|i|p_e) + c(|i|p_e + 2w)$$

The total crosstalk noise coefficient is the summation of coefficients from neighboring pairs

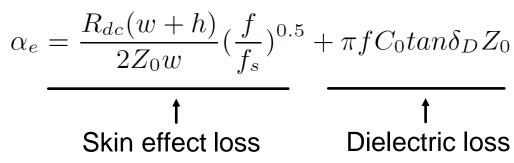

#### **Electrical Interconnect Attenuation**

- The attenuation factor of PCB trace has two terms, which are skin effect loss and dielectric loss

- $R_{dc}$  direct current resistance

- $Z_0$  characteristic impedance

- $f_s$  frequency of half skin depth

- $C_0$  the capacitance per unit length

- $tan\delta_D$  loss tangent in dielectric material

- The total attenuation of electrical interconnects

- $\eta_e$  coupling loss of electrical pin

- f working frequency

- L interconnect length

$$A_e = \frac{\eta_e^2 e^{-\alpha_e L}}{1 - 1}$$

Coupling loss Propagation loss

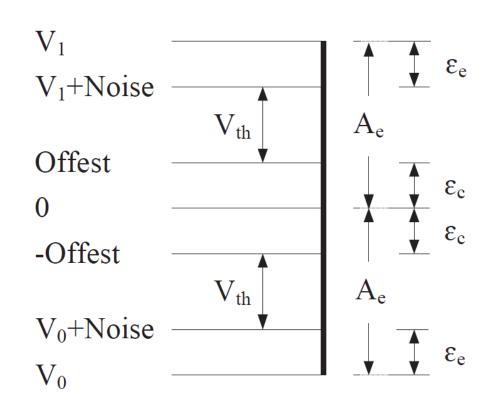

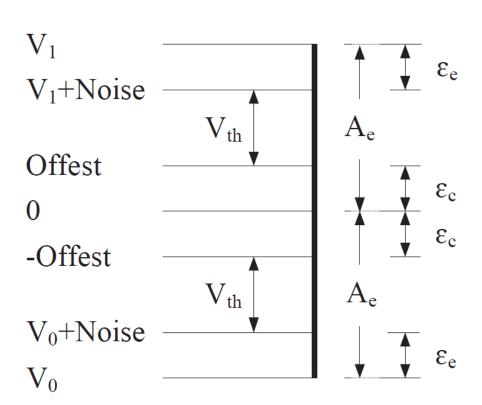

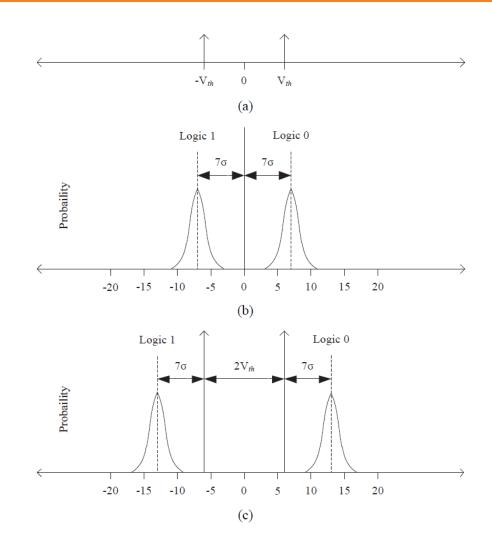

## **Electrical Interconnect Sensitivity**

- Only when this voltage difference is grater than |V<sub>th</sub>| of the limiting amplifier signals can be detected

- $A_e$  attenuation (0~1)

- $\varepsilon_e$  crosstalk noise coefficient

- $\varepsilon_o$  receiver offset coefficient:

- The supply current of driver

- $V_{th}$  threshold voltage

- $Z_d$  differential impendence

$$I_0 = \frac{2V_{th}}{(A_e - \epsilon_e - \epsilon_0) \cdot Z_d}$$

Ratio=

$$A - \varepsilon_e - \varepsilon_c = \Delta \varepsilon > 0$$

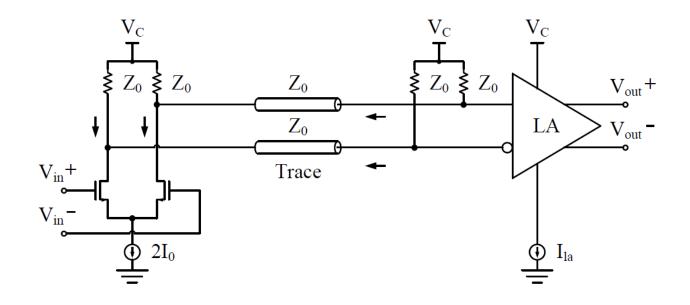

#### **Electrical Interconnect Power Consumption**

- In electrical interconnect, power consumption includes the power of driver, receiver and SerDes

- $P_{sd}$  power of SerDes

- $V_c$  supply voltage

- I<sub>la</sub> supply current of limiting amplifier

$$P_e = P_{sd} + (2I_0 + I_{la})V_c$$

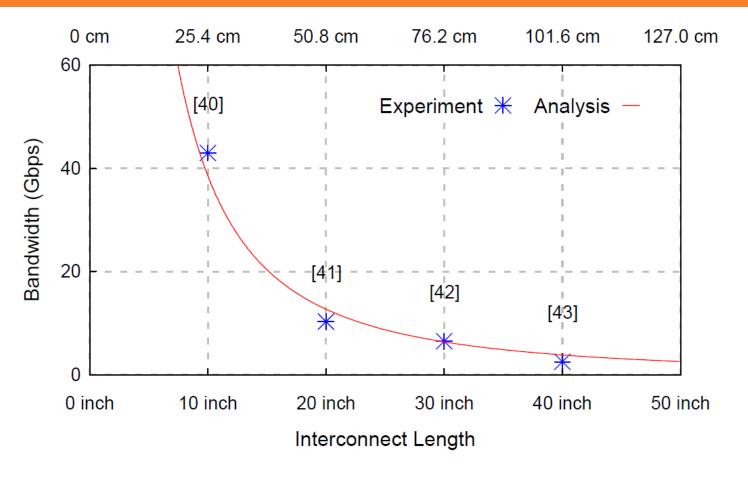

#### **Electrical Interconnect Bandwidth**

• If the signal frequency or the interconnect length is increased, trace attenuation is increased. The ratio  $\Delta\epsilon$  of the receiver amplitude over transmitter amplitude, will be decreased

$$A - \varepsilon_e - \varepsilon_c = \Delta \varepsilon$$

The maximum bandwidth of electrical interconnect

$$B_e = 2A^{-1}\left(-\frac{\ln(\varepsilon_e + \varepsilon_c + \Delta\varepsilon)}{L}\right)$$

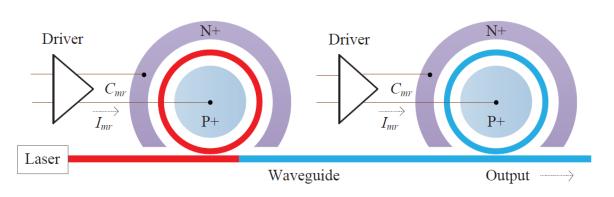

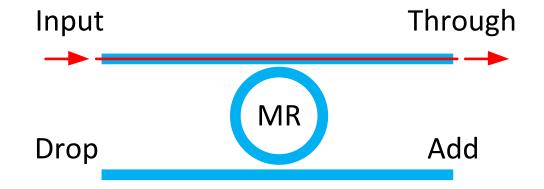

#### Microresonator

- Power of driver P<sub>d</sub>: each time the voltage level of the PN junction is reversed, it is charged or discharged by the driver

- $C_m$  input capacitance

- $V_m$  supply voltage

- Power of microresonator P<sub>m</sub>: when the voltage level of the PN junction is high, it is forward biased

- /<sub>m</sub> static current

$$P_d = f \cdot C_m \cdot V_m^2$$

$$P_m = I_m \cdot V_m$$

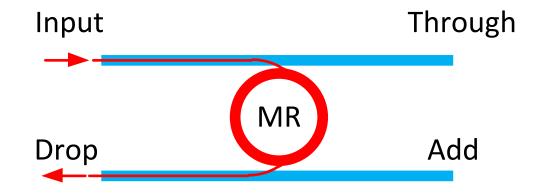

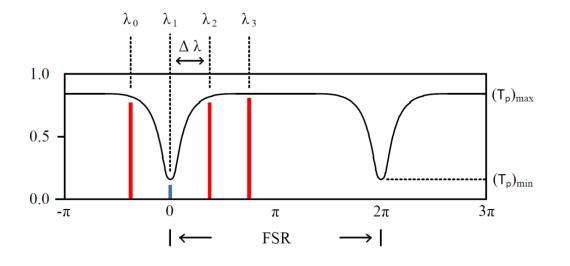

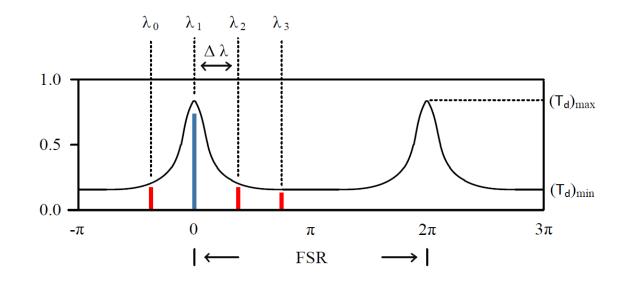

#### Optical Crosstalk Noise

At the receiver side, there are multiple optical signals in different wavelengths

$$\bullet$$

$\lambda_0$  ,  $\lambda_1$  ,  $\lambda_2$  ....  $\lambda_n$

■ Part of the signal power in wavelength  $\lambda_0$ ,  $\lambda_2$  and  $\lambda_3$  will also appear on the drop port

#### Optical Crosstalk Noise

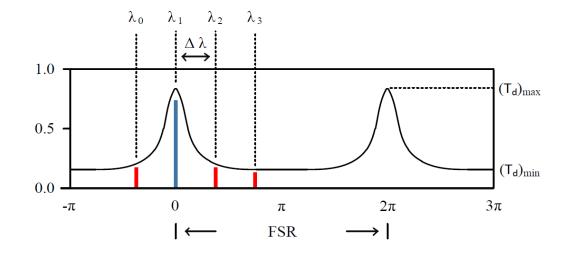

- In micro-resonator with working wavelength  $\lambda_1$ , the drop port transfer function is

- $cos\theta(\lambda)$  function of working frequency  $\lambda$

- r power splitting ratio

- *a* round trip attenuation

$$T_d(\lambda) = \frac{(1 - r^2)^2 a}{1 - 2r^2 a \cos \theta(\lambda) + r^4 a^2}$$

- $\blacksquare$  The optical crosstalk noise coefficient is the summation of unwanted signals whose wavelength is not  $\lambda_1$

- $m_o$  number of wavelengths in optical interconnect

- △ wavelength spacing

$$\varepsilon_o = 2 \sum_{i=1}^{\lfloor m_o/2 \rfloor} T_d^N(\lambda_1 + i\Delta\lambda)$$

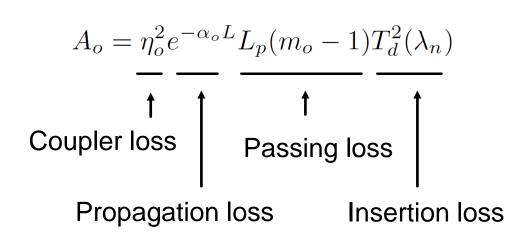

### Optical Interconnect Attenuation

- Before  $\lambda_0$  reaches the filter, it will pass by other micro-resonators with working wavelength

- $\bullet$   $\lambda_1$ ,  $\lambda_2$  ....  $\lambda_n$

- The attenuation of optical path is the product of:

- Coupler efficiency

- Propagation attenuation

- Passing-by loss of MR

- Insertion loss of MR

### Optical Interconnect Attenuation

• In microresonator with working frequency  $\lambda_1$ , the through port transfer function is

$$T_p(\lambda) = \frac{r^2 a^2 - 2r^2 a \cos\theta + r^2}{1 - 2r^2 a \cos\theta(\lambda) + r^4 a^2}$$

- The attenuation of optical path is the product of four terms

- $\eta_o$  coupling efficiency of optical pin

- *a<sub>o</sub>* attenuation of waveguide

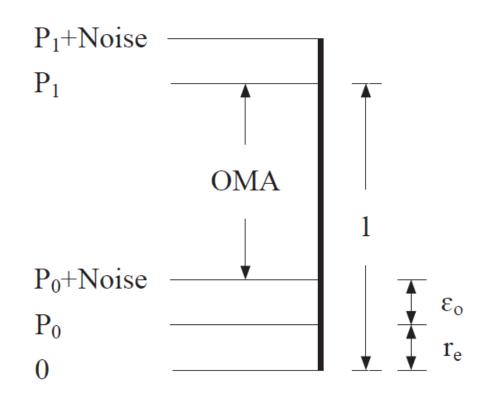

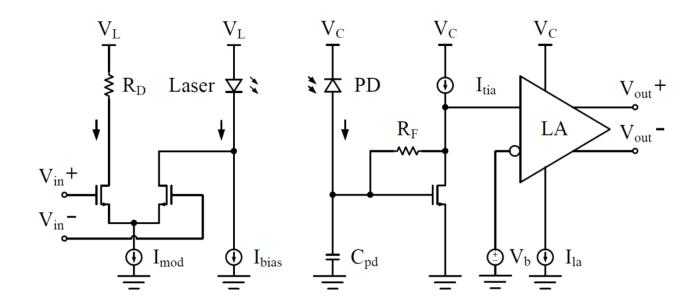

## Optical Interconnect Sensitivity

- In optical interconnect, the sensitivity OMA is the difference between two optical power levels P<sub>1</sub> and P<sub>0</sub>

- **BER** bit error rate

- *SNR* signal to noise ratio

- $i_n$  input referred RMS noise density

- $Z_{tia}$  transimpedance of TIA

- $\rho$  responsivity of photodetector

$$OMA = \frac{i_n f^{0.5} \cdot SNR + 2V_{th} Z_{tia}^{-1}}{\rho}$$

## Optical Interconnect Sensitivity

- Only when this voltage difference is grater than OMA, signals can be detected by the limiting amplifier

- $\varepsilon_o$  crosstalk noise coefficient

- $r_e$  extinction ratio  $P_1/P_0$

- $\eta_s$  slope efficiency of laser

- I<sub>th</sub> threshold current of laser

$$I_{mod} + I_{bias} = \frac{\text{OMA}}{A_o(1 - \varepsilon_o - r_e)\eta_s} + I_{th}$$

Ratio=

$$1 - \varepsilon_o - r_e > 0$$

#### Optical Interconnect Bandwidth

- FSR is the spacing between two successive resonance peaks in spectrum

- $n_e$  MR effective refractive index

- R MR radius of ring

$$FSR = \frac{\lambda^2}{2\pi n_e R}$$

Δλ is the wavelength spacing between two neighboring wavelengths

$$\mathbf{B}_o = 2 \lfloor \frac{\mathbf{FSR}}{\Delta \lambda} \rfloor f$$

### Optical Interconnect Power Consumption

- In optical interconnect, power consumption includes the power of laser sources, receiver, SerDes and modulator

- $V_l$  laser supply voltage

- *I<sub>tia</sub>* TIA supply current

- Direct modulation

$$P_o = P_{sd} + (I_{mod} + I_{bias})V_l + (I_{tia} + I_{la})V_c$$

Indirect modulation

$$P_{o} = P_{sd} + (I_{mod} + I_{bias})V_{l} + (I_{tia} + I_{la})V_{c} + P_{m} + P_{d}$$

## Optical Interconnect Power Consumption and Area

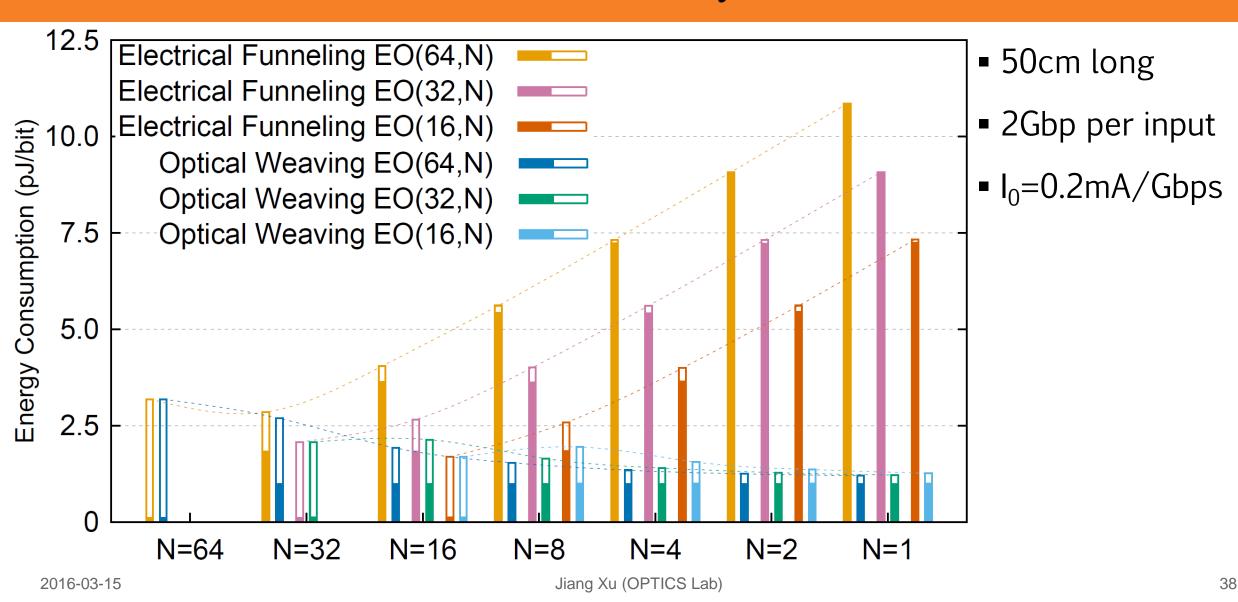

The power consumptions of the electrical funneling interface and optical weaving interface

$$P_{feo} = 5log_2 RP_e + P_c + \frac{1}{4}P_d + \frac{1}{2}P_m + P_t + \frac{P_o}{L_i} \qquad P_{weo} = P_e + P_c + \frac{1}{2}P_d + RP_m + RP_t + \frac{P_o}{L_i^R}$$

The areas of the electrical funneling interface and optical weaving interface

$$S_{feo} = 5log_2 R S_e + S_c + S_m + S_l$$

$$S_{weo} = \frac{M}{2N} S_e + S_c + \frac{M}{N} S_m + S_l$$

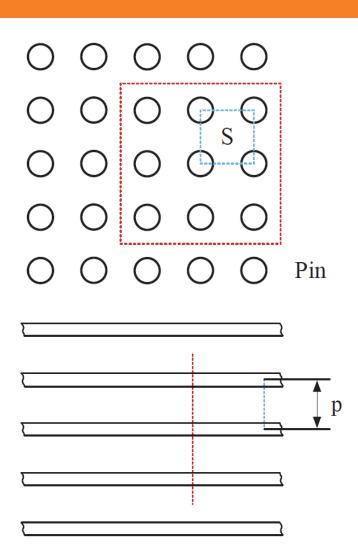

## Area and Linear Bandwidth Density

- Area bandwidth density

- Bandwidth in a unit area

- Important to package pin, socket etc.

Area Density =

$$\frac{\text{Bandwidth } B}{\text{Area } S}$$

- Linear bandwidth density

- Bandwidth in a unit width

- Important to PCB, substrate, interposer *etc.*

$$Linear Density = \frac{Bandwidth B}{Pitch p}$$

Interconnect

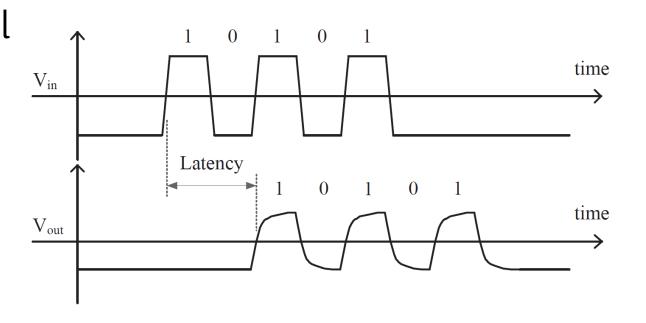

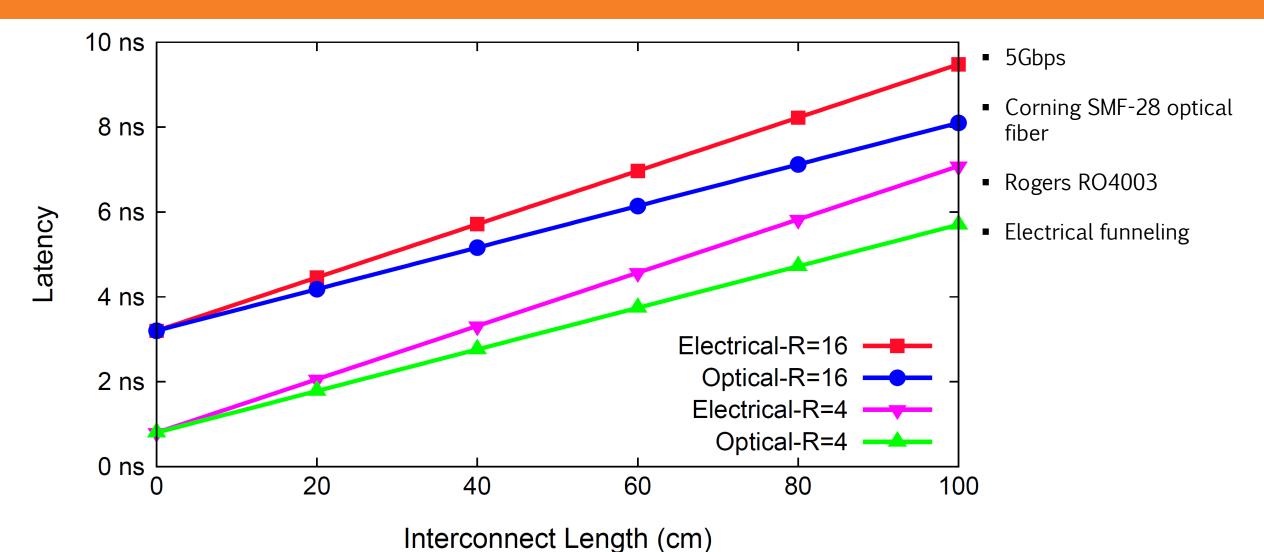

## Electrical and Optical Interconnect Latency

- Propagation delay is proportional to the interconnect length, and inverse proportional to the propagation speed

- $V_e$  speed in electrical interconnect

- $\epsilon_r$  relative dielectric constant

$$v_e = \frac{c}{\sqrt{\epsilon_r}}$$

- $V_c$  speed in optical interconnect

- $n_g$  group reflection index

$$v_o = \frac{c}{n_g}$$

#### Serializer and Deserializer

- SerDes consist of multiple stages of multiplexers or demultiplexers

- With a large number of latches

- A bottleneck in inter-chip interconnect

- Large power consumption, large area, additional latency

#### **Electrical Interconnect Verification**

Our analytical models match experiment results well

## Traditional OE Interface: Electrical Funneling

Electrical SerDes plus O-E conversion

## New OE Interface: Optical Weaving

#### Optical-electrical SerDes

#### Outline

- Introduction

- Modelling of off-chip interconnects and interfaces

- Electrical Interconnects

- Optical Interconnects

- SerDes and O-E interface

- A new O-E interface

- Quantitative analysis and comparisons

- Conclusions

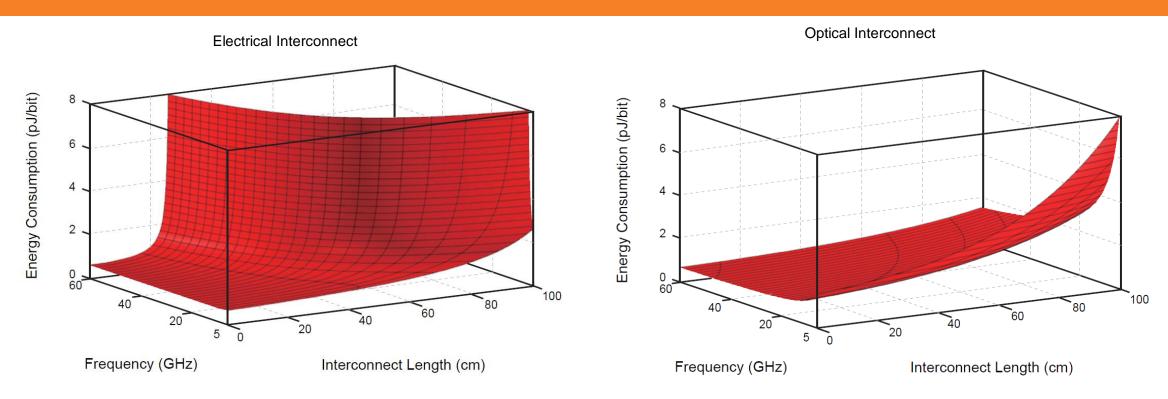

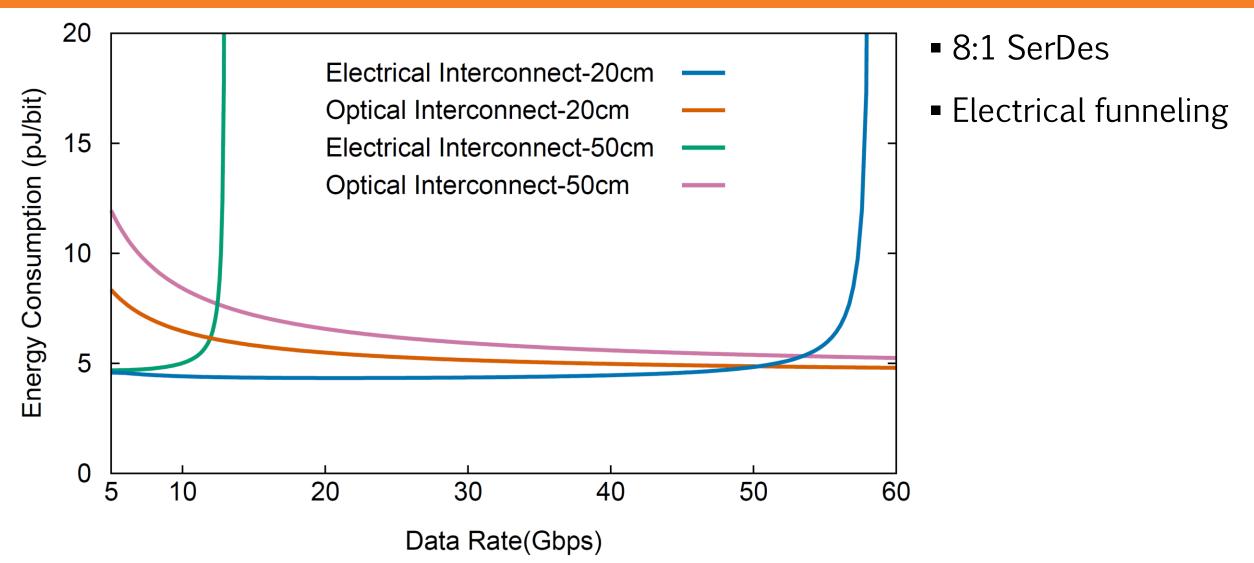

## Optical vs. Electrical Interconnect: Energy Efficiency

- Electrical interconnect has an energy cliff

- Optical interconnect favorite high data rate

## Optical vs. Electrical Interconnect: Energy Efficiency

2016-03-15 Jiang Xu (OPTICS Lab) 34

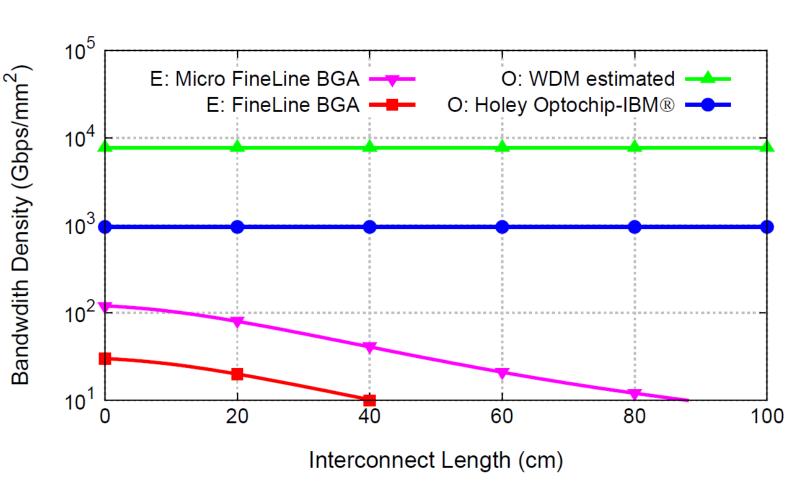

## Optical vs. Electrical Interconnect: Area Bandwidth Density

- Two orders of magnitude higher than micro-FBGA package

- Three orders of magnitude higher than FBGA package

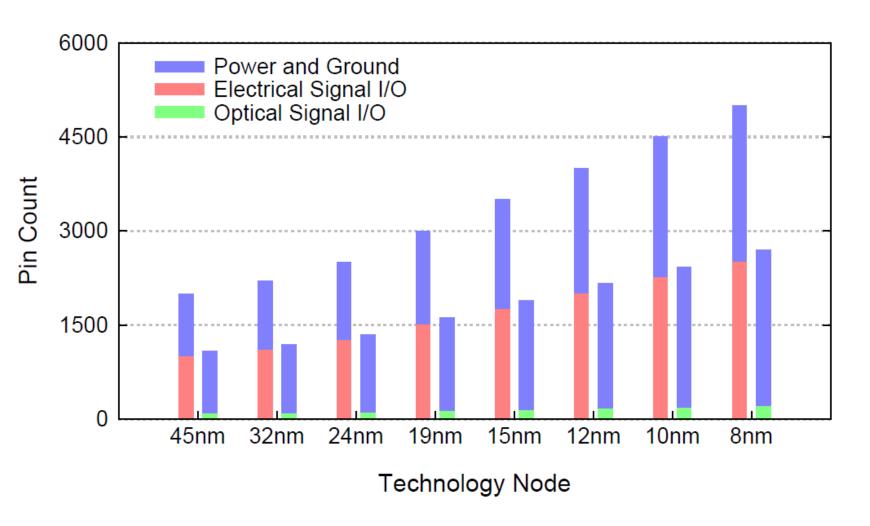

#### Optical vs. Electrical Interconnect: Pin Count

- Reduce >92% signal pins with 25cm interconnects

- Reduce >97% signal pins with 50cm interconnects

## Optical vs. Electrical Interconnect: Latency

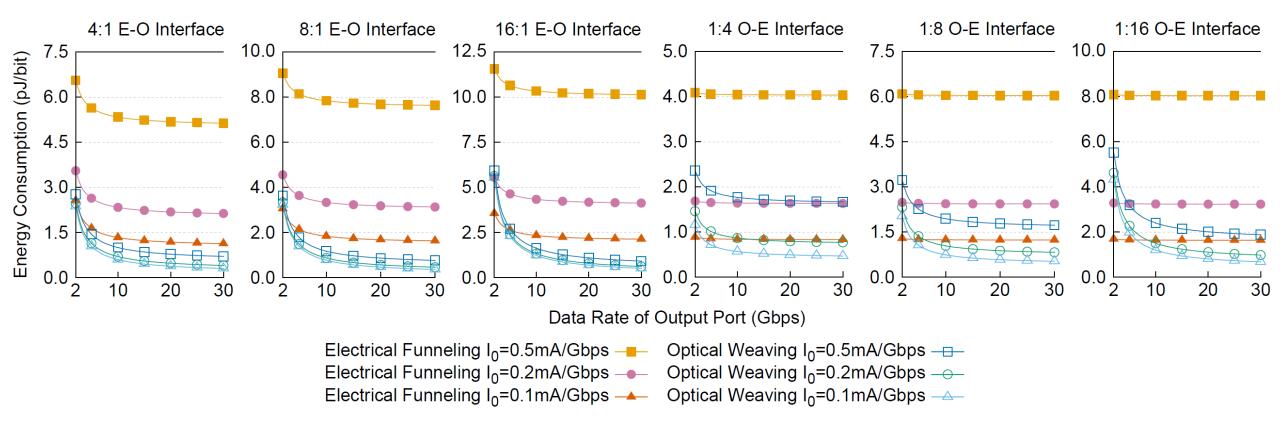

## Optical Weaving vs. Electrical Funneling: Energy Efficiency

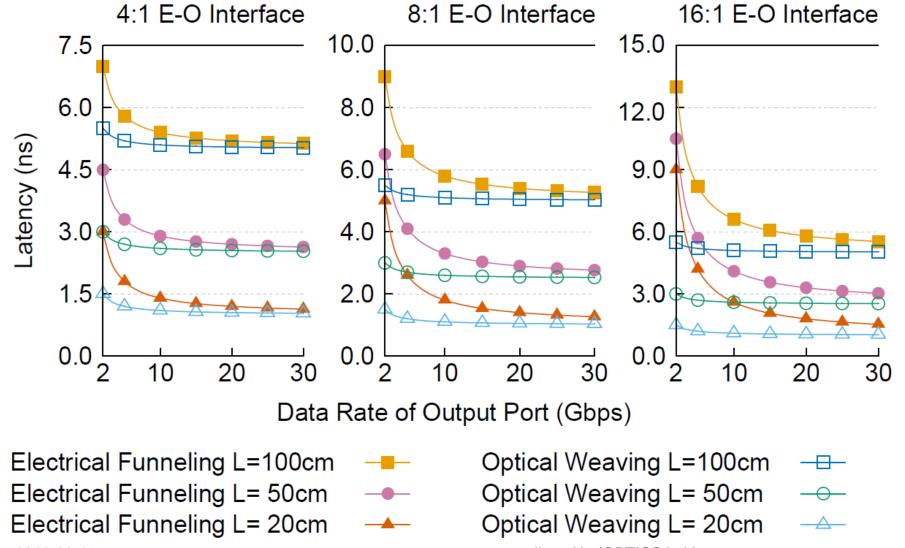

## Optical Weaving vs. Electrical Funneling: Latency

•  $I_0$ =0.2mA/Gbps

Jiang Xu (OPTICS Lab)

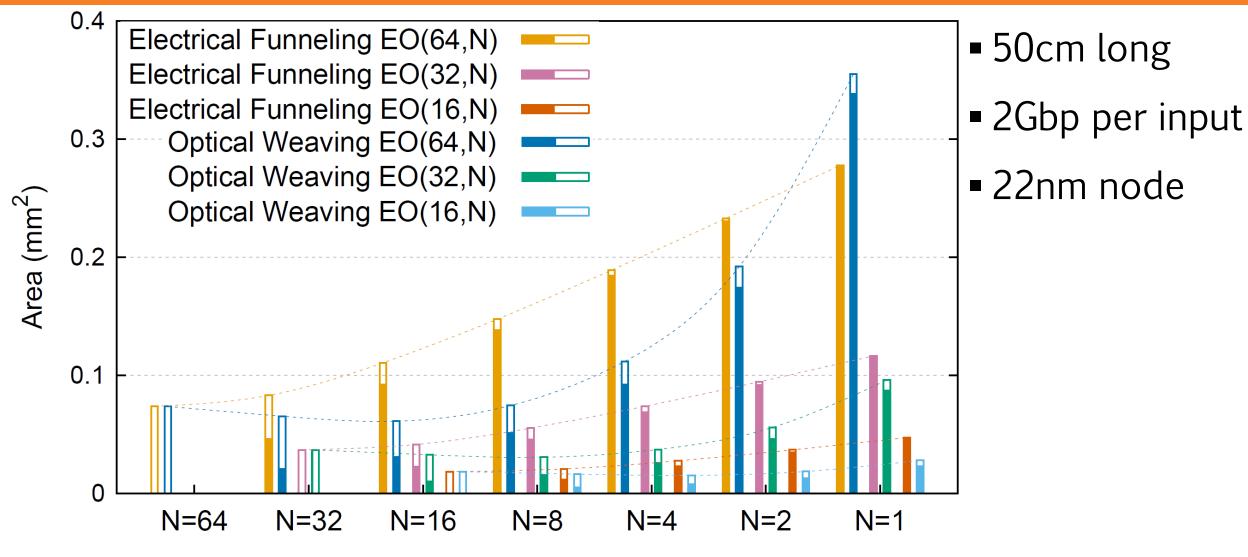

## Optical Weaving vs. Electrical Funneling: Area

2016-03-15 Jiang Xu (OPTICS Lab) 4

## Optical Weaving vs. Electrical Funneling: Technology Dependency

Differences in circuit design details, technology nodes, and foundry processes are reflected by unit current I<sub>0</sub>

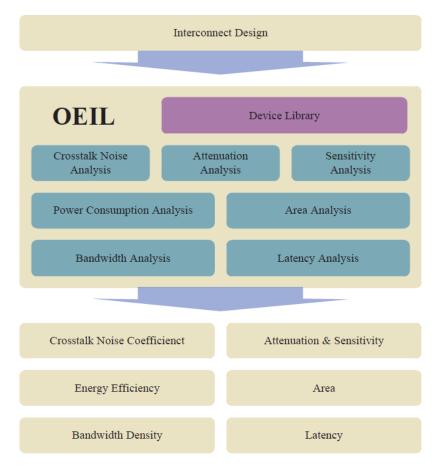

#### OEIL: Optical and Electrical Interfaces and Links

- A comprehensive device library for off-chip interconnects

- Publicly released and available at

www.ece.ust.hk/~eexu/OEIL.html

The flow chart of OEIL simulator

#### Conclusions

- Analytical models for optical and electrical interconnects and interfaces

- Holistic comparisons in terms of bandwidth, bandwidth density, latency, energy efficiency, signal integrity, and area

- Proposed a new O-E interface, optical weaving

- Publicly released a R&D tool, OEIL

#### References

- [1] PCI-SIG, "PCI Express 4.0 evolution to 16GT/s, twice the throughput of PCI Express 3.0 technology," Technical Publication, 2011.

[2] D. Brooks, "Crosstalk coupling: single-ended vs. differential," Technical Publication, 2005.

[3] F. Doany, C. Schow, C. Baks, D. Kuchta, P. Pepeljugoski, L. Schares, R. Budd, F. Libsch, R. Dangel, F. Horst, B. Offrein, and J. Kash, "160 Gb/s bidirectional polymer-waveguide board-level optical interconnects using CMOS based transceivers," Advanced Packaging, IEEE Transactions on, vol. 32, no. 2, pp. 345–359, 2009.

[4] C. Schow, F. Doany, A. Rylyakov, B. Lee, C. V. Jahnes, Y. Kwark, C. Baks, D. Kuchta, and J. Kash, "A 24-channel, 300 Gb/s, 8.2 pJ/bit, full-duplex fiber-coupled optical transceiver module based on a single "Holey" CMOS IC," Lightwave Technology, Journal of, vol. 29, pp. 542–553, Feb 2011.

[5] "Optical and Electrical Interfaces and Links (OEIL)." [Online]. Available: http://www.ece.ust.hk/~eexu.

[6] H. Cho, P. Kapur, and K. Saraswat, "Power comparison between highspeed electrical and optical interconnects for inter-chip communication," in Interconnect Technology Conference, 2004.

[7] G. Chen, H. Chen, M. Haurylau, N. A. Nelson, D. H. Albonesi, P. M. Fauchet, and E. G. Friedman, "Predictions of CMOS compatible onchip optical interconnect," Integration, the VLSI Journal, vol. 40, no. 4, pp. 434 446, 2007, 13 8 M. R. Feldman, S. C. Esener, C. C. Guest, and S. H. Lee, "Comparison between optical and electrical interconnects based on power and speed considerations," applied optics, vol. 27, no. 9, pp. 1742-[9] Y.-P. Lee and Y. Zhang, "Performance comparison and overview of different approaches for vlsi optoelectronic interconnects," Optical Communications and Networking, IEEE/OSA Journal of, vol. 2, pp. 206–220, April 2010. E101 E. Berglind, L. Thylen, B. Jaskorzynska, and C. Svensson, "A comparison of dissipated power and signal-to-noise ratios in electrical and optical interconnects," Lightwave Technology, Journal of, vol. 17, pp. 68–73, Jan 1999.

[11] F. Sellaye, F. Caignet, and J. Collet, "Comparison of optical and electrical interconnects for intrachip communications," in Signal Propagation on Interconnects, 6th IEEE Workshop on. Proceedings, pp. 12] J. Shin, C.-S. Seo, A. Chellappa, M. Brooke, A. Chattejce, and N. Jokerst, "Comparison of electrical and optical interconnect," in Electronic Components and Technology Conference, 2003. Proceedings. 53rd, pp. 1067–1072, May 2003.

[13] Z. Wang, J. Xu, P. Yang, X. Wang, Z. Wang, L. Duong, Z. Wang, H. Li, R. Maeda, X. Wu, Y. Yaoyao, and Q. Hao, "Alleviate chip I/O pin constraints for multicore processors through optical interconnects," in Design Automation Conference (ASP-DAC), 2015–20th Asia and South Pacific, pp. 791–796, Jan 2015. [14] E. Bogatin, "A closed form analytical model for the electrical properties of microstrip interconnects," Components, Hybrids, and Manufacturing Technology, IEEE Transactions on, vol. 13, pp. 258–266, Jun 1990. Jun 1990.

15] R. Ho, K. Mai, and M. Horowitz, "The future of wires," Proceedings of the IEEE, vol. 89, pp. 490–504, Apr 2001.

16] A. Poon, X. Luo, F. Xu, and H. Chen, "Cascaded microresonator-based matrix switch for silicon on-chip optical interconnection," Proceedings of the IEEE, vol. 97, pp. 1216–1238, July 2009.

17] D. Miller, "Device requirements for optical interconnects to silicon chips," Proceedings of the IEEE, vol. 97, pp. 1166–1185, July 2009.

18] K. Ohashi et al., "On-chip optical interconnect," Proceedings of the IEEE, vol. 97, pp. 1186–1198, July 2009.

19] P. Heydari and R. Mohanavelu, "Design of ultrahigh-speed low-voltage CMOS CML buffers and latches," Very Large Scale Integration Systems, IEEE Transactions on, vol. 12, pp. 1081–1093, Oct 2004.

20] Texas Instruments, "Flip chip ball grid array package reference guide," Technical Publication, 2005.

21] D. Taillaert, F. Van Laere, M. Ayre, W. Bogaerts, D. Van Thourhout, P. Bienstman, and R. Baets, "Grating couplers for coupling between optical fibers and nanophotonic waveguides," Japanese Journal of Applied Physics, vol. 45, no. 8R, p. 6071, 2006.

22] Corning Incorporated, "Corning R single-mode optical fiber," Technical Publication, 2007.

23] E. Bogatin, Signal and power integrity-simplified, Pearson Education, 2009.

24] Saturn, "PCB Design Toolkit." http://www.saturnpcb.com/pcb toolkit. htm, 2013.

25] M. Jouppi, "Design specifications-a review of IPC-2152, current carrying capacity for printed board design,," Printed Circuit Design and Fab, vol. 26, no. 7, p. 17, 2009.

26] Q. Xu, B. Schmidt, S. Pradhan, and M. Lipson, "Micrometre-scale silicon electro-optic modulator," Nature, 2005.

27] W. Bogaerts, P. De Heyn, T. Van Vaerenbergh, K. De Vos, S. Kumar Selvaraja, T. Claes, P. Dumon, P. Bienstman, D. Van Thourhout, and R. Baets, "Silicon microring resonators," Laser and Photonics Reviews, vol. 6, no. 1, pp. 47–73, 2012.

#### References

[28] S. C. Thierauf, High Speed Circuit Board Signal Integrity. Artech House, 2004.

[29] Intel Corporation, "Performance characteristics of IC packages," Technical Publication, 2000.

[30] W. J. Dally and J. W. Poulton, Digital systems engineering. Cambridge university press, 1998.

[31] Maxim Integrated, "Accurately estimating optical receiver sensitivity," Technical Publication, 2001.

[32] W. Hofmann et al., "1.55 μm InP-based VCSEL with enhanced modulation bandwidths » 10 GHz up to 85 °C," in OFC, 2009.

[33] S. Assefa, F. Xia, W. M. J. Green, C. Schow, A. Rylyakov, and Y. Vlasov. "CMOS-integrated optical receivers for enaching intercents." S. Assefa, F. Xia, W. M. J. Green, C. Schow, A. Rylyakov, and Y. Vlasov, "CMOS-integrated optical receivers for on-chip interconnects," Selected Topics in Quantum Electronics, IEEE Journal of, vol. 16, 1376–1385, Sept 2010. Altera Corporation, "Designing with high-density BGA packages for Altera devices," Technical Publication, 2014.

| Rogers Corporation, "RO4000 R series high frequency circuit materials," Technical Publication, 2013.

| E. Holzman, "Wideband measurement of the dielectric constant of an FR4 substrate using a parallel-coupled microstrip resonator," Microwave Theory and Techniques, IEEE Transactions on, vol. 54, pp. 36E. Holzman, "Wideband measurement of the dielectric constant of an FR4 substrate using a parallet-coupled microstrip resonator, microwave (Ineory and Techniques, IEEE Transactions on, vol. 34, pp. 4004-4015, Dec 2013.

37E. Brillouin, Wave propagation and group velocity, Academic Press, 1960.

38R. Kinoshita, K. Moriya, K. Choki, and T. Ishigure, "Polymer optical waveguides with GI and W-shaped cores for high-bandwidth-density on-board interconnects," Lightwave Technology, Journal of, vol. 31, pp. 4004-4015, Dec 2013.

38B. Olinop, "Multilayer PCB stackup planning," Technical Publication, 2011.

40H. Barnes, "ATE interconnect performance to 43 Gbps using advanced PCB materials," Technical Publication, 2008.

41Altera, Modeling and design considerations for 10 Gbps connectors," Technical Publication, 2010.

42B. Sevcik, "High-speed serial differential signaling links with commercial equalizer," in 20th International Conference, pp. 1-4, April 2010.

43B. Extractive Semiconductor Corporation, "High-speed PCB design considerations," Technical Publication, 2011.

44 "International technology roadmap for semiconductors," Semiconductor Industry Association, http://publicitrs.net.

45F. Doany, C. Schow, C. Basko, D. Kuchta, P. Pepeliugoski, L. Schares, R. Budd, F. Libor, R. Dangel, F. Horst, B. Offrein, and J. Kash, "160 Gb/s bidirectional polymer-waveguide board-level optical merconnects sing CMOS-based transceivers," Advanced Packaging, IEEE Transactions on, vol. 32, no. 2, pp. 345-359, 2009.

45P. Schuffer, J. T. Mechler, M. A. Sorna, K. Dramstad, C. R. Oglive, A. Mohamman and J. D. Rockorich, High Speed SerDes Devices, and Applications. Springer, 2008.

45P. Spring A. D. Ellis, and Publication, D. T. Murphy, S. J. Savage, and L. P. Rockorich, High Spring Seed SerDes Devices, and Applications. Springer, 2008.

45P. Spring A. D. Ellis, and Publication, D. J. Savage, and L. P. Rockorich, High Springer, and L. P. Rockorich, High Springer, and J. D. Rockorich, High Springer, and J. D. Rockorich, High Springer, 2013. 3127–3130, Julý 2006. [58] W.-Y. Tsai, C.-T. Chiu, J.-M. Wu, S. Hsu, and Y.-S. Hsu, "A novel low gate-count pipeline topology with multiplexer-flip-flops for serial link," Circuits and Systems I: Regular Papers, IEEE Transactions on, vol. 59, pp. 2600–2610, Nov 2012.

#### References

[59] K.-Y. Park, W.-Y. Choi, S.-Y. Lee, and W.-S. Oh, "A 6.24-Gb/s wide-input-range serializer ASIC using fixed-data-rate scheme," in Circuits and Systems (ISCAS), 2012 IEEE International Symposium on. pp. [60] F. Tobajas, R. Esper-Chain, R. Regidor, O. Santana, and R. Sarmiento, "A low power 2.5 Gbps 1:32 deserializer in SiGe BiCMOS technology," in Design and Diagnostics of Electronic Circuits and systems, 2006 IEEE, pp. 19–24, April 2006.

[61] H.-W. Huang, C.-Y. Wang, and J.-Y. Jou, "An efficient heterogeneous tree multiplexer synthesis technique," Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on, vol. 24, pp. 1622–1629, Oct 2005. [62] J. Maneatis, J. Kim, I. McClatchie, J. Maxey, and M. Shankaradas, "Selfbiased high-bandwidth low-jitter 1-to-4096 multiplier clock generator PLL," Solid-State Circuits, IEEE Journal of, vol. 38, pp. 1795-1803, Nov 2003. 1603, NoV 2003.

[63] S. Feng, T. Lei, H. Chen, H. Cai, X. Luo, and A. W. Poon, "Silicon photonics: from a microresonator perspective," Laser & photonics reviews, vol. 6, no. 2, pp. 145–177, 2012.

[64] M. Fukaishi, K. Nakamura, M. Sato, Y. Tsutsui, S. Kishi, and M. Yotsuyanagi, "A 4.25-Gb/s CMOS fiber channel transceiver with asynchronous tree-type demultiplexer and frequency conversion architecture," solid-State Circuits, IEEE Journal of, vol. 33, pp. 2139–2147, Dec 1998.

[65] T. Suzuki, Y. Kawano, Y. Nakasha, S. Yamaura, T. Takahashi, K. Makiyama, and T. Hirose, "A 50-Gbit/s 450-mW full-rate 4:1 multiplexer with multiphase clock architecture in 0.13μm InP HEMT technology," Solid-State Circuits, IEEE Journal of, vol. 42, pp. 637–646, March 2007.

[66] M. Khafaji, C. Carta, E. Sobotta, D. Micusik, and F. Birolay and Mode Logic Springer 2005. [67] A. Massimo and P. Gaetano, Model and Design of Bipolar and MOS Current-Mode Logic. Springer, 2005.

[68] S. Rylov, S. Reynolds, D. Storaska, B. Floyd, M. Kapur, T. Zwick, S. Gowda, and M. Sorna, "10+ Gb/s 90-nm CMOS serial link demoin CBGA package," Solid-State Circuits, IEEE Journal of, vol. 40, pp. 1987–1991, Sept 2005. 1987-1991, Sept 2005.

[69] A. Tanabe, M. Umetani, I. Fujiwara, T. Ogura, K. Kataoka, M. Okihara, H. Sakuraba, T. Endoh, and F. Masuoka, "0.18-µm CMOS 10-Gb/s multiplexer/demultiplexer ICs using current mode logic with tolerance to threshold voltage fluctuation," Solid-State Circuits, IEEE Journal of, vol. 36, pp. 988-996, Jun 2001.

[70] Maxim Integrated, "Accurately estimating optical receiver sensitivity," Technical Publication, 2001.

[71] A. Mutig, High Speed VCSELs for Optical Interconnects. Springer, 2011.

[72] O. Xu, B. Schmidt, S. Pradhan, and M. Lipson, "Micrometre-scale silicon electro-optic modulator," Nature, vol. 435, no. 7040, pp. 325–327, 2005.

[73] Y. Zhang, Y. Li, S. Feng, and A. Poon, "Towards adaptively tuned silicon microring resonators for optical networks-on-chip applications," Selected Topics in Quantum Electronics, IEEE Journal of, vol. 20, pp. 136-149, July 2014.

[74] P. Dong, S. Liao, D. Feng, H. Liang, D. Zheng, R. Shafiiha, C.-C. Kung, W. Qian, G. Li, X. Zheng, A. V. Krishnamoorthy, and M. Asghari, "Low Vpp, ultralow-energy, compact, high-speed silicon electro-optic modulator," Opt. Express, vol. 17, pp. 22484–22490, Dec 2009.

[75] X. Zheng, E. Chang, I. Shubin, G. Li, Y. Luo, J. Yao, H. Thacker, J.-H. Lee, J. Lexau, F. Liu, P. Amberg, K. Raj, Ho, J. Cunningham, and A. Krishnamoorthy, "A 33mW 100Gbps CMOS silicon photonic WDM transmitter using off-chip laser sources," in OFC/NFOEC, pp. 1–3, March 2013.

[76] R. J. Baker, CMOS: Circuit Design, Layout, and Simulation, vol. 18. John Wiley & Sons, 2011.

[77] R. Mekky and M. Dessouky, "A 08-6.3 GHz spread spectrum clock generator for SerDes transmitter clocking," in Microelectronics (ICM), 2010 International Conference on, pp. 80–83, Dec 2010.

[78] Q. Xu, S. Manipatruni, B. Schmidt, J. Shakya, and M. Lipson, "12.5 Gbit/s carrier-injection-based silicon micro-ring silicon modulators," Opt. Express, vol. 15, pp. 430–436, Jan 2007.

[79] J. Cunningham, I. Shubin, X. Zheng, T. Pinguet, A. Mekis, and A. Krishnamoorthy, "Highly-efficient thermally-

2016-03-15 Jiang Xu (OPTICS Lab) 4

217–218, July 2010.

[80] B. Schwank and K. Nellis, "NRZ-to-RZ data conversion using highspeed OR/AND," Electronic Products, pp. 48–49, Jan 2009.

[81] L. Brillouin, Wave Propagation and Group Velocity. Academic Press, 1960.

[82] Corning Incorporated, "Corning R single-Mode optical fiber," Technical Publication, 2007.