# Laser Integration challenges For on-chip optical interconnects

Y. Léger, C. Cornet, R. Tremblay, I. Lucci, O. Durand Foton Laboratory, CNRS unit, Rennes, France

## **ENSSAT**

LANNION

Optical communications & sensors

Materials for photonics

# ENSSAT

LANNION

Optical communications & sensors

Materials for photonics

#### Monolithic silicon photonics

Where?

The best place of the photonic layer in a microprocessor

Hows

The best integration approach of active photonic devices

What?

The best laser design for a given MP architecture

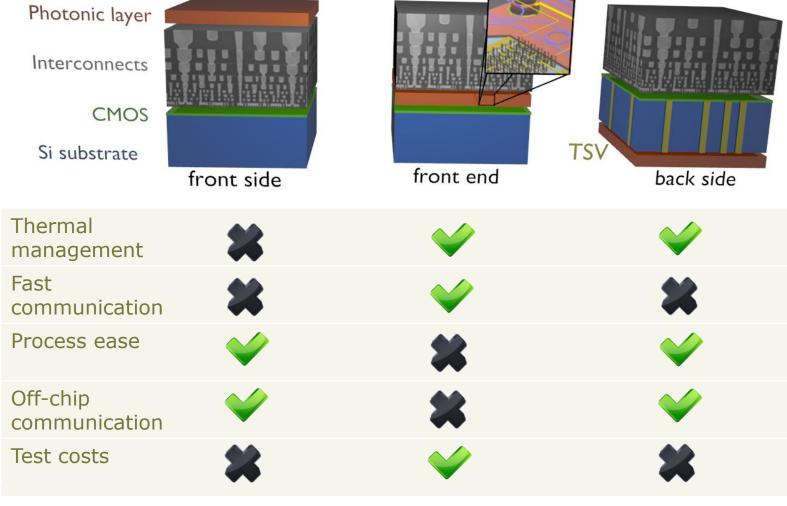

## Where?

## Very different approaches by the electronics giants

#### IBM:

Co-integration of CMOS and photonics

Combined front-end integration

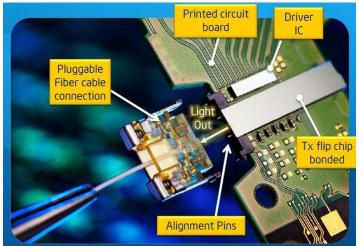

#### Intel:

Front side bonding of III-V lasers on Si

# Where?

## At the fab line level:

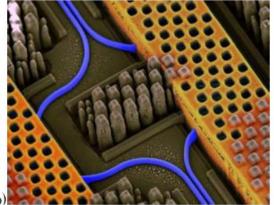

### In 3D architectures:

Inspired from N. Solomon patent US8136071 B2

photonic layer

**FPGA**

**CMOS** logic

Memory

**DSP**

Memory

Analog

- New issues for thermal management

- Is the previous classification still relevant?

- Always production-line-related considerations

- Consequences at different abstraction levels of the architecture design

• Huge issues related to the integration method...

Nat. Phot. '15

Gent Univ.

Nat. Phot. '16

**Foton**

Foton

Group IV photonics (Si, Ge, GeSn)

CMOS compatibility

Laser electric drive

In some cases the wavelength

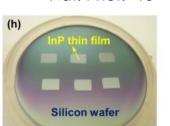

• Heterogeneous integration of III-V

Process and architecture

III-V wafer issue

Best(?) yields

(large scale integration, costs)

Flexibility

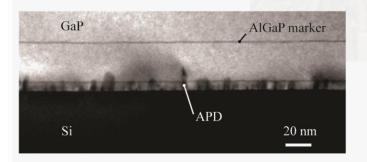

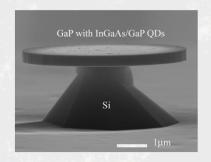

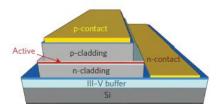

Metamorphic integration of III-V

Large scale integration

Pseudo-substrate issue

Good yields

Thermal management

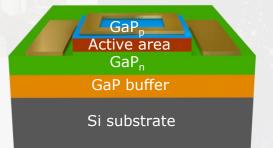

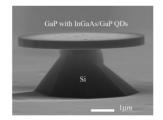

Pseudomorphic integration of III-V

Large scale integration

Optical property immaturity

Best choice for combined

front-end

Thermal management

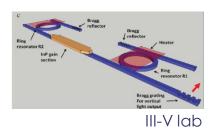

## What?

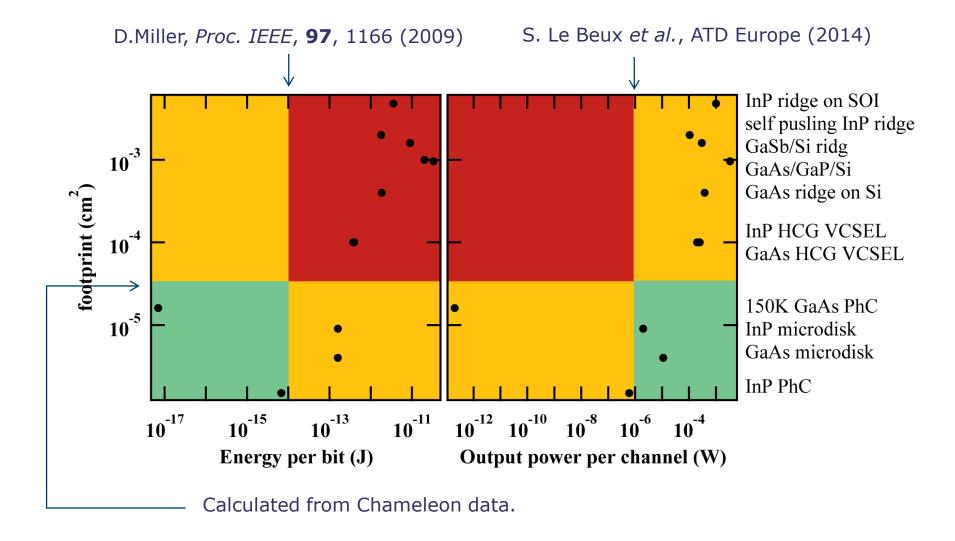

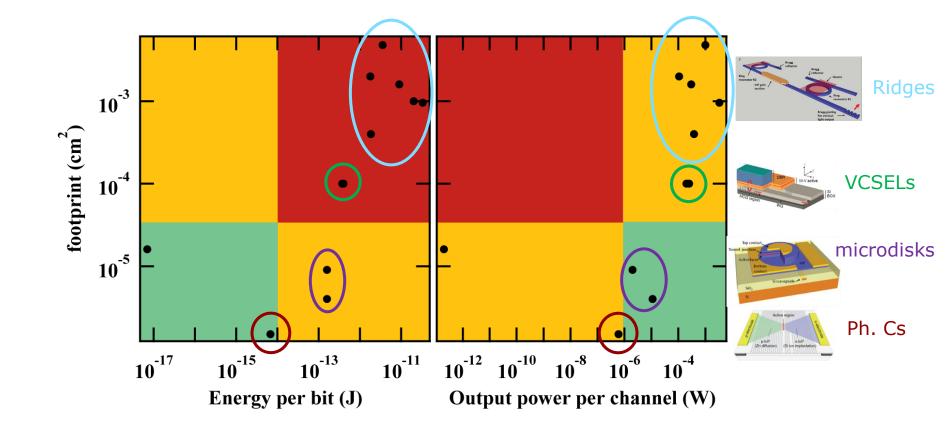

# Four kinds of laser designs:

#### Ridge lasers

Microdisks/rings

Ph. C. cavities

**VCSELs**

## Different demands in PICs:

#### Corona archi.

- -External optical drive

- high power laser (0.8W)

- WDM source

- no footprint issue

#### Chameleon archi.

- -thousands of on-chip micro-lasers

- -Low power source

- tunability?

- huge footprint constraint

# What?

# What?

- 1) Integration issues at the chip scale

- The ultimate monolithic integration might not be so unreachable

- 3) No laser solution so far: PhCs, microdisks or power sharing of ridges or VCSELs

All the issues, no solutions in ...

Integrated lasers on Silicon

(C. Cornet, Y. Léger, C. Robert)

To be published (ISTE/Elsevier)