# Model electro-optical integrated circuits using Verilog-A

Dr. Zeqin Lu

R&D Manager – Photonics IC Solutions

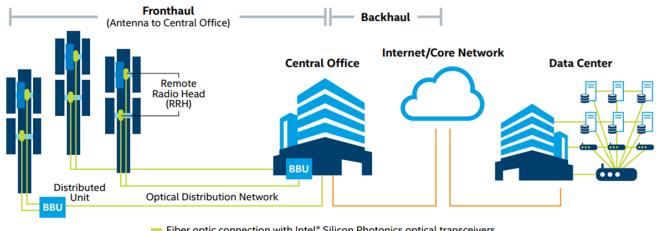

### Photonics is a Key Enabler of 5G, Data Centers, Al and More

Fiber optic connection with Intel® Silicon Photonics optical transceivers

Dense wavelength division multiplexing (DWDM) fiber optic connections

Source: "Exploring 5G Fronthaul Network Architecture Intelligence Splits & Connectivity" 5G Wireless Communications - Silicon Photonics, Intel

High Performance Computing | Ayar Labs In-Package

https://ayarlabs.com/high-performance-computing/

https://spectrum.ieee.org/techtalk/computing/hardware/building-quantum-computerswith-photons

Image: Xiaogang Qiang/University of Bristol

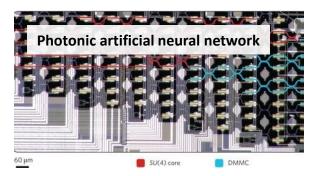

Y. Shen et al. Deep learning with coherent nanophotonic circuits, Nature Photonics, https://doi.org/10.1038/nphoton.2017.93

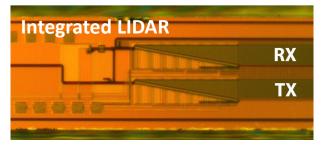

MIT and DARPA Pack Lidar Sensor Onto Single Chip https://spectrum.ieee.org/techtalk/semiconductors/optoelectronics/mit-lidar-on-a-chip Image: Christopher V. Poulton

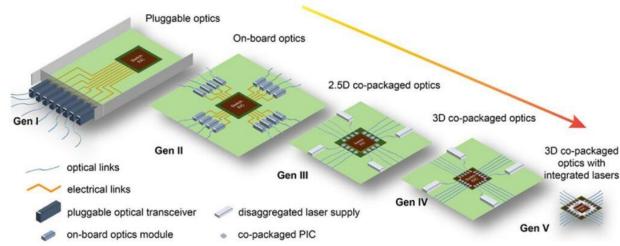

### The trends...

- The rising demands for compute power;

- Optical interconnects will continue to replace copper to bring the power consumption down.

- Photonic packaging evolves quickly and moves towards 3DIC

- Challenges:

- Signal integrity: EIC & PIC should be co-designed to optimize their overall performance

- Thermal integrity

- Optical I/O

Ref: "Perspective on the future of silicon photonics and electronics" N. Margalit, et.al., Appl. Phys. Lett. 118, 220501 (2021)

# Agenda

- Basic: model optical signal using Verilog-A

- Advanced photonic Verilog-A models

- Create Verilog-A models through automation

- Example: 4-ch DWDM SiP transceiver design

- Key takeaway

# **Basics of photonic Verilog-A**

**/**Insys

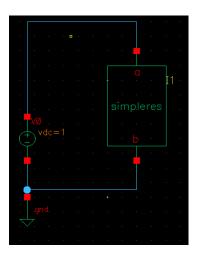

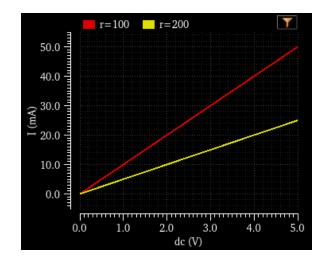

### What is Verilog-A model?

- Verilog-A models are analog behavior models that can be solved by SPICE circuit solvers.

- Verilog-A model behavior and ports can be customized by script.

- Compatible with various electrical analyses (dc, ac, tran)

```

module simpleres(a, b);

inout a, b;

electrical a, b;

parameter real r = 1000 from (0:inf);

analog begin

I(a,b) <+ V(a,b) / r;

end

endmodule</pre>

```

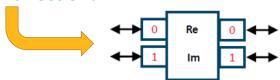

### How to simulate optical signal using Verilog-A?

- Electrical signal includes potential and flow

- Optical signal is complex (Re & Im), frequency-dependent, mode-dependent, and bidirectional.

- Workaround:

- Optical signal is represented by buses

- Each port is a structured port

- Analytically describe input-to-output signal transmission (single directional)

```

include "../../../cad/constants.vams"

'include "../../../cad/disciplines.vams"

module Optical_Waveguide(inLight, outLight);

inout [0:3] leftLight; // [0:1] is left side input, [2:3] is left side output

inout [0:3] rightLight; // [0:1] is right side output [2:3] is right side input. optical

[0:3] rightLight, leftLight;

// Physical Design Parameters, all units in SI

parameter real L = 0.0005;

// length

parameter real ng = 4.1963;

// group index

parameter real np = 2.1;

// refractive index

parameter real alphaA = 287.6; // loss

parameter real G freq = 1.93e14; // reference frequency parameter passed in from

top level simulation

// initialize intermediate points

optical [0:1] rightOutput;

optical [0:1] leftOutput;

optical [0:1] transfer, // for calculated phase-shift and amplitude change

optical [0:1] transferCart; // for above in real and imaginary forms

pol2cart convs1(transfer, transferCart); // convert waveguide effect to real and

cartmul mulout1(transferCart, leftLight[0:1], rightOutput); //Calc outputs

cartmul mulout1B(transferCart, rightLight[2:3], leftOutput);

analog begin

//calculate phase-shift and amplitude change in polar coordinates

E(transfer[0]) <+ (-L*np*2*'M PI*G freq/'P C)%(2*'M PI);

E(transfer[1]) \le exp(-alphaA*L);

// Output delayed signals

E(rightLight[0]) <+ absdelay(E(rightOutput[0]), L*ng/`P C);

E(rightLight[1]) <+ absdelay(E(rightOutput[1]), L*ng/P C);

E(leftLight[2]) <+ absdelay(E(leftOutput[0]), L*ng/`P C)

E(leftLight[3]) <+ absdelay(E(leftOutput[1]), L*ng/P C);

endmodule

```

C. Sorace-Agaskar, et. al.,, "Electro-optical co-simulation for integrated CMOS photonic circuits with VerilogA," Opt. Express 23, 27180-27203 (2015)

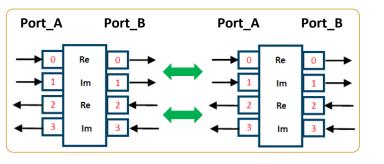

### Photonic SPICE/Verilog-A challenges

#### **Challenge 1**

- Male/Female type unidirectional ports are widely used in photonic Verilog-A model, making schematic connection very restricted.

- Ansys' Solution: Bi-directional ports

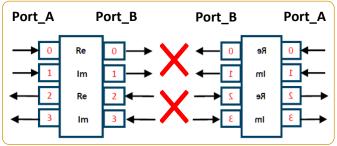

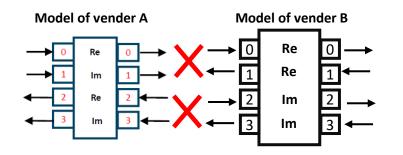

#### **Challenge 2**

- No industry standards for optical port interface!

- Possible solution: IEEE Working Group P3186

#### **Challenge 3**

- Creating model requires a lot of model expertise

- Maintaining/updating complex models with hundreds/thousands lines of code is time-consuming.

- Ansys' solution: Automated model compiler!

# Advanced photonic Verilog-A models

**Ansys**

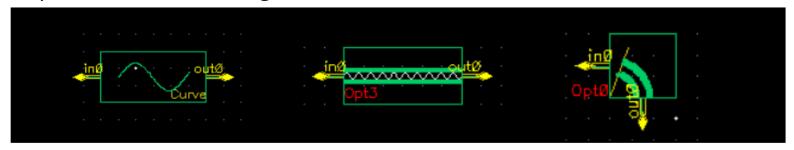

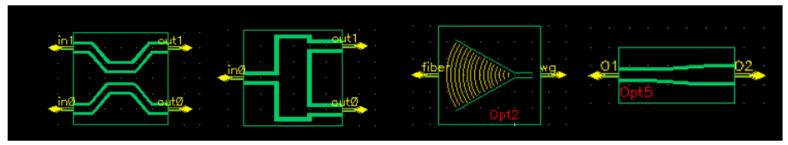

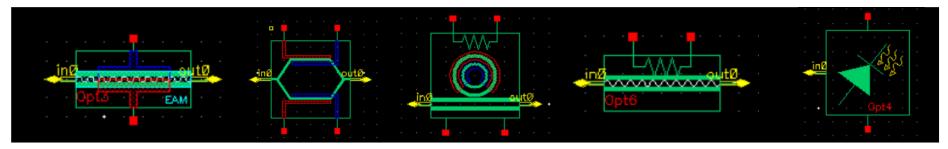

## Mode library overview

• Waveguides: Fixed and parameterized waveguides

• Couplers: Fixed and parameterized couplers based on S-parameters, grating and directional couplers

• Actives: Electrical/thermal phase shifters, ring modulators, Mach-Zehnder modulators, EAMs and photodetectors

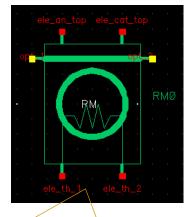

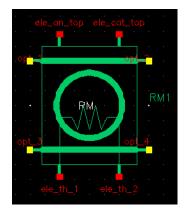

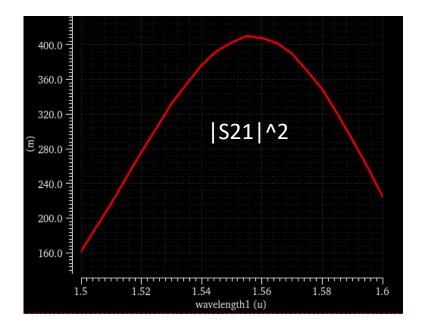

# Ring modulator

#### Model source data:

- Ring radius

- Coupler data

- Waveguide neff, ng, loss

- Thermal tuner data

- Carrier-depletion/injection tuner data

- Electrical RC parameters

- etc...

#### All-pass ring modulator

#### Add-drop ring modulator

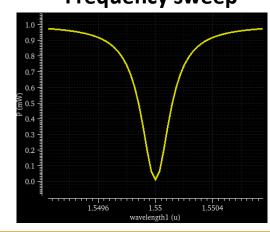

#### Frequency sweep

Compile

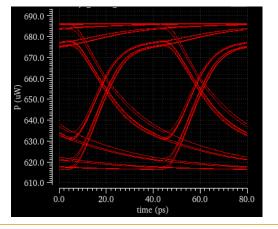

#### Time-domain modulation

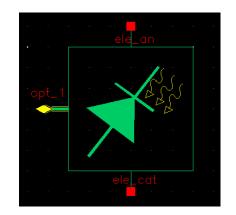

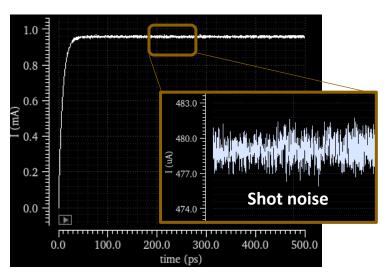

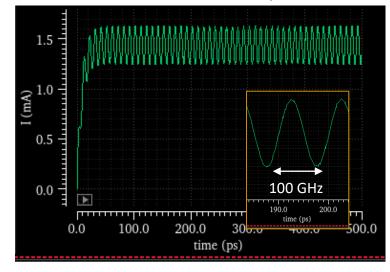

# Photodetector

#### Model source data:

- Frequency-dependent responsivity

- Voltage-dependent dark current

- Voltage-dependent net bandwidth

- Electrical RC parameters

- Enable/disable shot noise

- etc...

#### **Transient response (1-ch input)**

@1550 nm, 1mW

#### **Channel crosstalk**

- @1550 nm, 1mW

- @1550.8 nm, 1mW

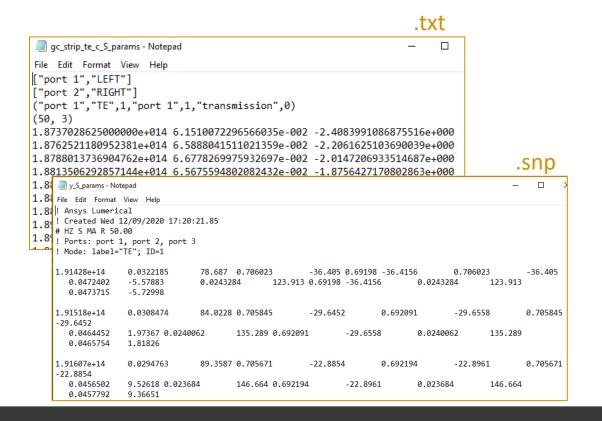

### S-parameter elements

- Model source data:

- Lumerical S-parameter data file

Compile

Touchstone S-parameter data file

How to create models through automation?

**/**Insys

### Compact model library (CML) compiler

Automates generation of photonic compact model libraries (CMLs)

**Component data collection Compact Model Generation Circuit/System Design** CML Compiler Measurement data Build Install Build Run Deploy **Photonic Verilog-A models** Lumfoundry Tests Library Element Status Center O X + Schematic symbols Compact Library master file /home/developer/Desktop/temp/my models/library.json ▼ Reload models Select Photonic Model Add Ring\_Mod\_C\_band ring\_modulator electro\_absorption\_modulator Delete photodetector simple Simulation data Rename layer group gopdk Si3N4 (Silicon Nit Clear gondk Cu (Conner) - CRI gopdk TiN - Palik geometry

CHARGE\_simulation\_region

CHARGE boundary conditions

C\_2D

layer group objects

# Let's see an example

**Ansys**

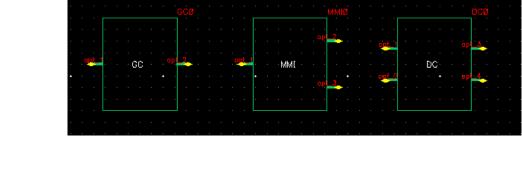

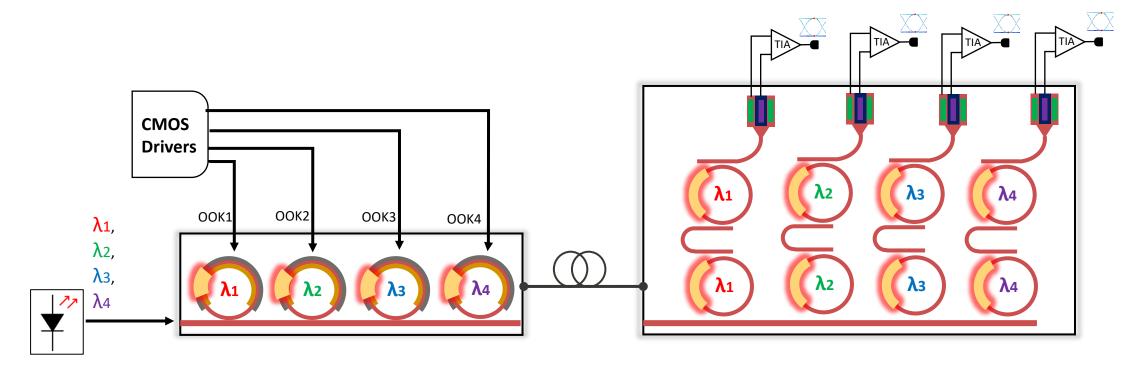

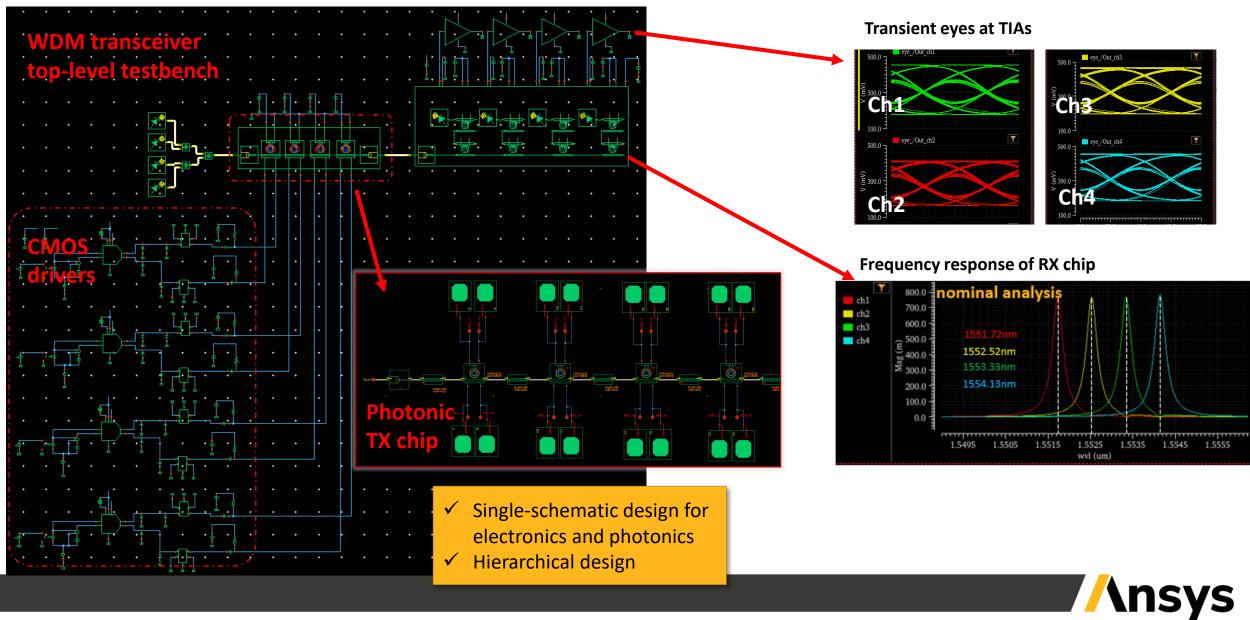

### Example – 4-channel DWDM Transceiver Design

Silicon photonic (SiP), ring-based, 4-channel DWDM transceiver design

• Channels: 1551.72nm, 1552.52nm, 1553.33nm, 1554.13nm

• **Data rate**: 25Gbps x 4 = 100 Gbps

## Schematic design & simulation

# Conclusion

- We presented the use of standard Verilog-A language for modeling advanced photonic components in PIC analysis, where complex, bidirectional, multimodal, and multiwavelength optical signal are fully supported.

- Photonic Verilog-A models are compatible with commercial SPICE solvers, making them ideal for EIC and PIC co-design and co-optimization.

- Ansys' CML Compiler can help creating Photonic Verilog-A models in automated approach.

- Model vendors and EDA vendors need to work together to create IEEE standards for optical port interface!

# Ansys